双路径,四级、三级,前导0检测(非预测,优先权、二分),booth补码乘法,舍入

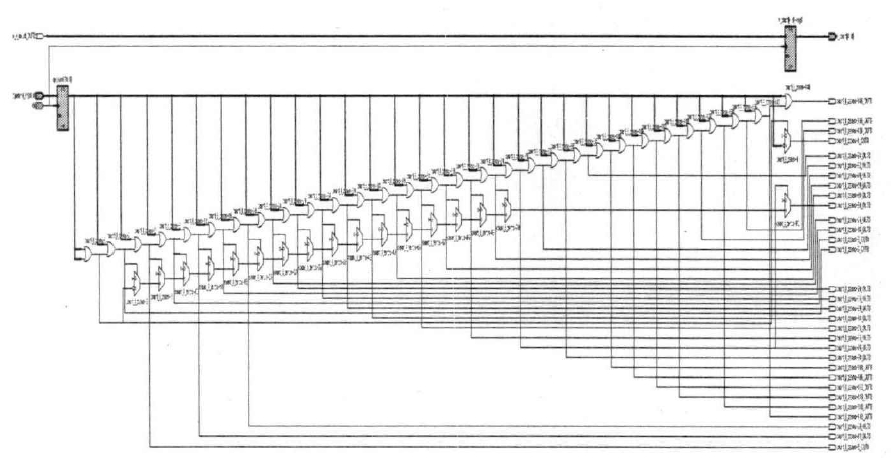

加法器结构

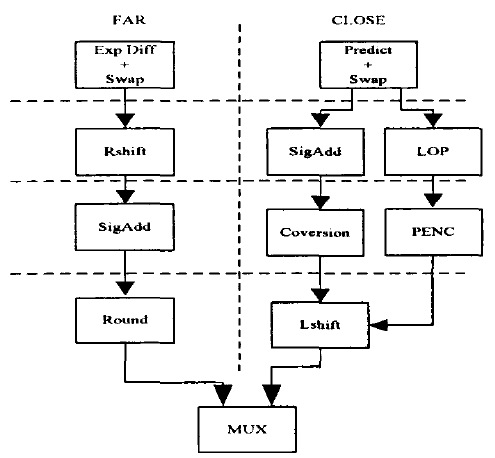

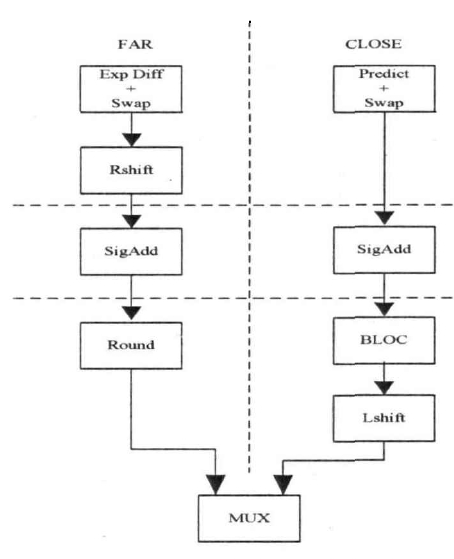

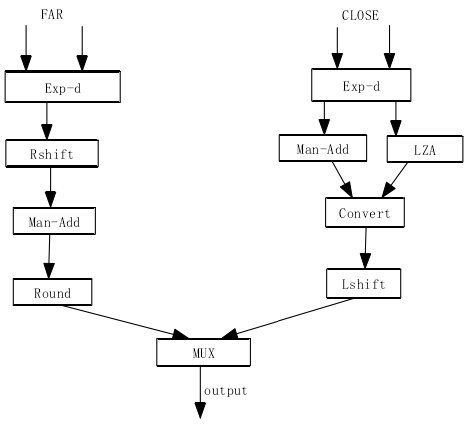

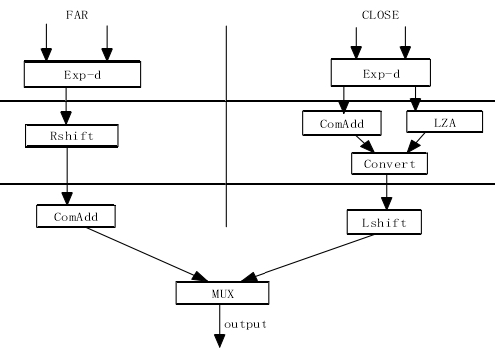

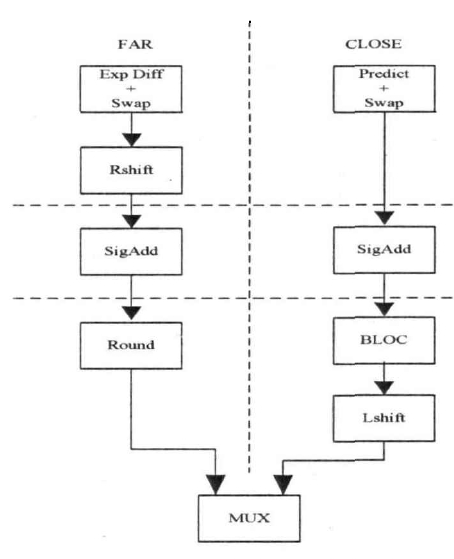

two - path

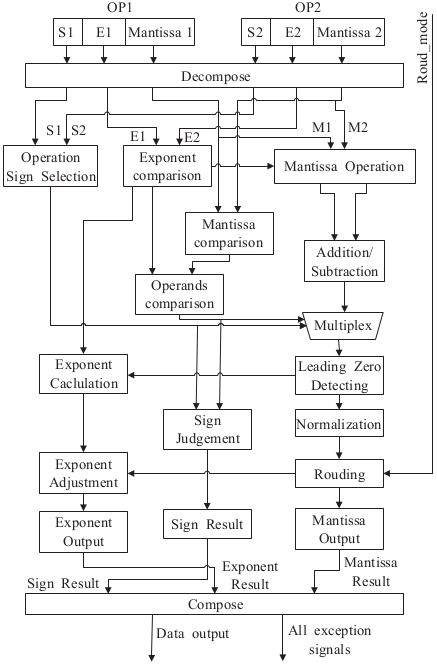

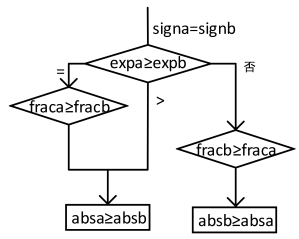

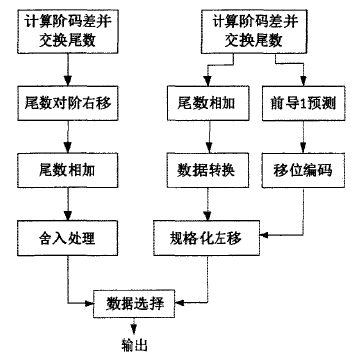

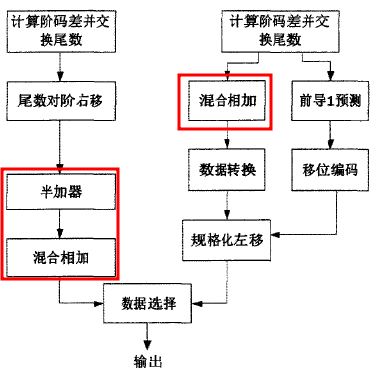

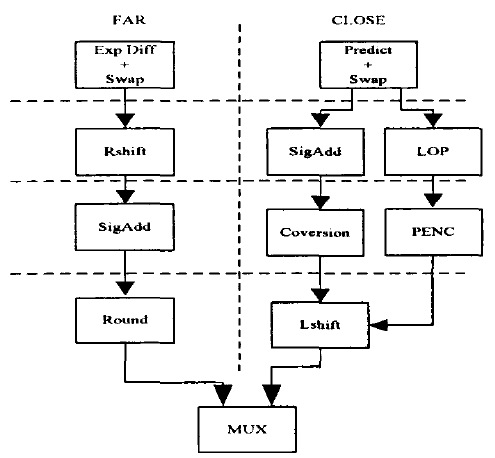

通路和通路当阶码差值小于等于1时,尾数运算结果规格化移位所需的时间比较长,而对阶移位所需时间比较短,称为CLOSE通路。

而当阶码相差大于1时,则结果规格化移位所需时间比较短,而对阶移位所需时间比较长,称为FAR通路。

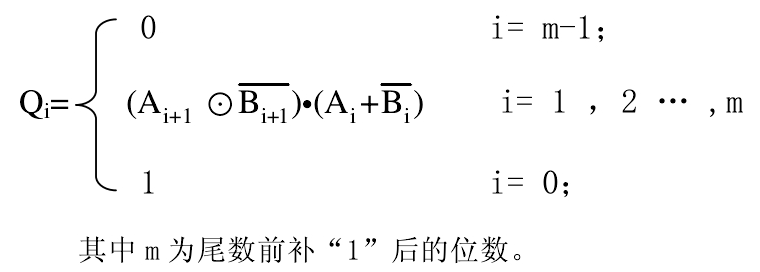

前导 0 预测

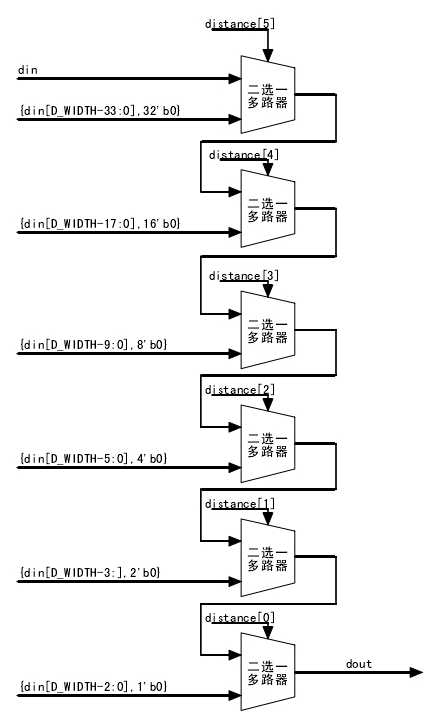

在对阶移位和规格化移位中,对阶移位的移位数直接由两个操作数的指数差值决定,而规格化移位的移位数必须通过对结果尾数进行检测才可以得到。

因此,规格化移位中的前导零的检测直接影响着浮点加法部件的性能。

针对前导零检测,人们运用部分压缩和重编码理论进行了前导零预判。在进行尾数加减操作的同时对操作数进行部分压缩和重编码从而预测结果尾数的前导零

个数。但是前导零预判技术硬件代价较大,电路逻辑复杂,所以在运用此技术的同时要考虑面积和功耗的因素。

在传统的方法中,规格化操作是在得到尾数加减的非规格化结果后进行的,这样做可以使实现方法变得简单。但是这种方法也存在一个问题,即增加了浮点运算的关键路径长度,加大了单元的延迟时间。

优先权判断

直接对结果从高位到低位进行一位一位的检测并记数,直到检测到最高位的为止。这种方法实现简单、直观。但是它存在延迟大,电路扇入扇出大,逻辑复杂的缺陷。

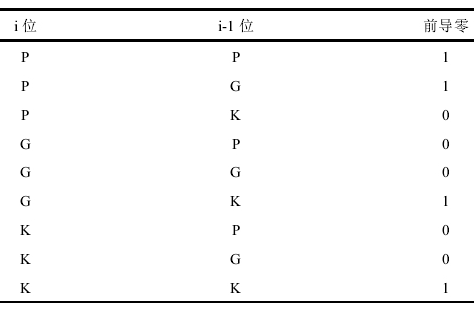

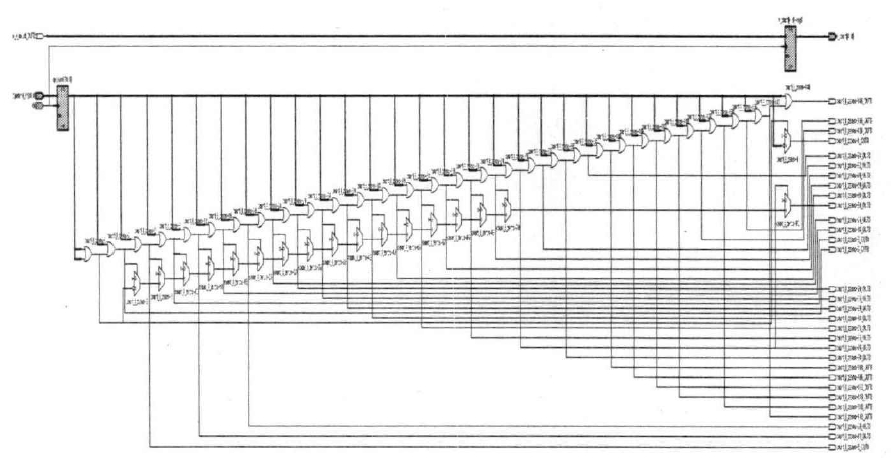

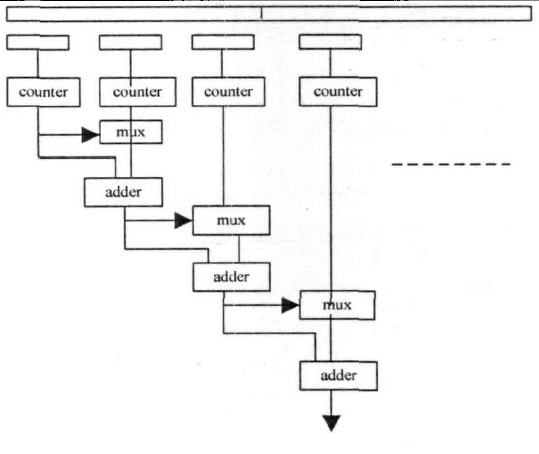

二分检测法

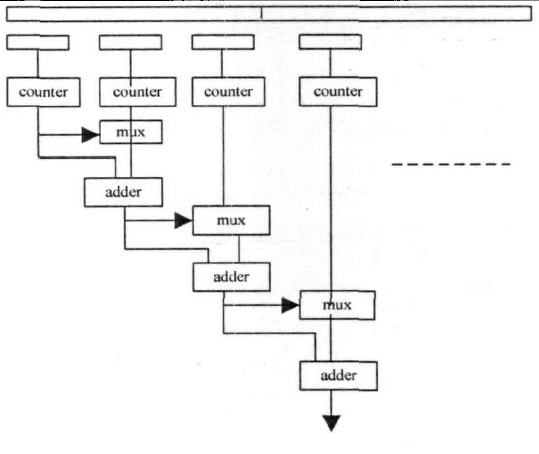

如果输入二进制串的左半子串是全零串,那么检测结果的最高有效位为,检测结果的剩余部分就是右半子串的检测结果。否则,检测结果的最高有效位为检测结果的剩余部分就是左半子串的检测结果。这个结论可以递归地应用于两个更小的子串。

二分检测法将大的二进制串分解成小的子串,各个子串的前导零检测同时进行,最后进行逻辑组合得到最终的前导零个数,解决了优先权编码检测器的大扇入扇出问题,简化了电路逻辑,优化了电路结构,并且更重要的是大大的提高了电路的工作速度。

尾数分割成的子串数越多,每个子串前导零检测时间越少,但是需要的加法器以及选择器就越多,各个子串的前导零数相加的时间就越大。为此要综合平衡子串个数以及由此产生的级数。

文中例子,划分为2个子串频率最高,划分为4个、8个则频率逐渐降低。

加法器结构设计

如果采用流水技术,一个浮点加法器可分成四级流水,完成一个浮点加法运算需要一个周期。但是在本文设计的中为了使的控制逻辑简单,保证操作顺序输入结果顺序输出,使浮点加法与乘法的三段流水一致,所以本文在一算法加法器的结构上对之进行结构改进。

在本文的设计中,将FAR通路中的耗时较少的操作数交换和尾数右移合二为一,在一个时钟周期内完成,对于CLOSE通路运用前导零的二分检测法可以将结果规格化和左移在一个时钟周内完成。

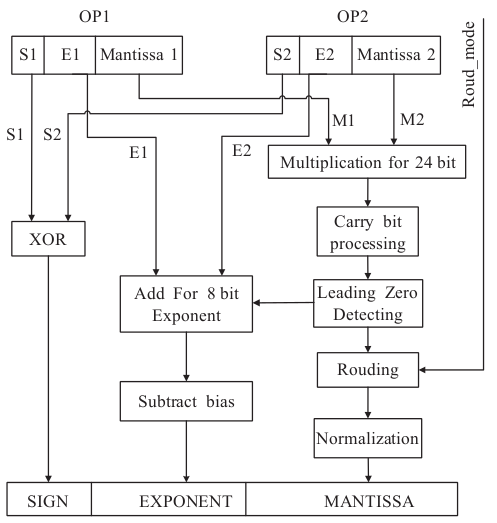

乘法器

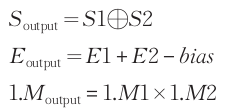

乘法流程

- 检测操作数是否为0,并设置结果数:如果操作数中有一个为 0 ,乘积必为 0 ,不必做其他操作;如果均不为0,方进行乘法运算。结果数符号按同号相乘为正,异号相乘为负的规则确定。

- 阶码相加。阶码相加可能产生溢出,应当注意。同号相加可能上溢,也可能下溢。此时要检测溢出异常,使得处理单元转入溢出处理。

- 尾数相乘。这可以用任何一种定点小数乘法实现

- 乘法规格化。尾数相乘后,可能需要右规。由于尾数是定点小数(非规格数?),相乘后不会出现需要左规的情况。右规是阶码加,有上溢的可能。

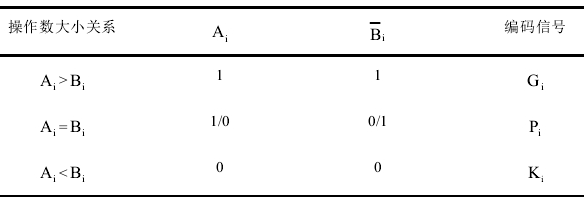

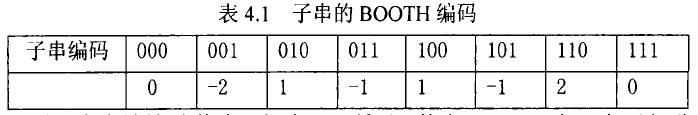

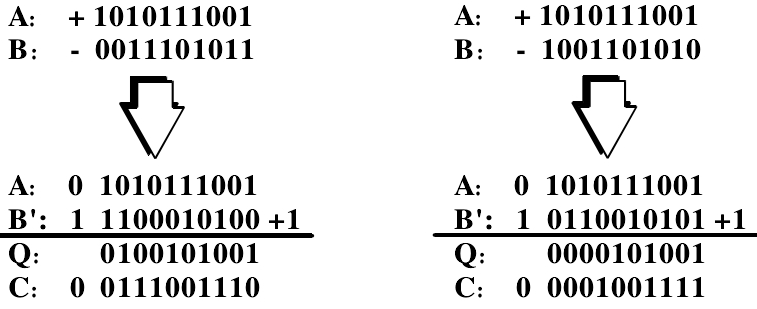

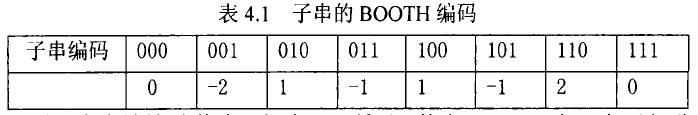

Booth

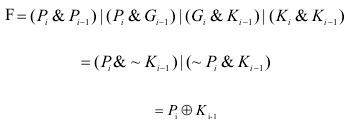

算法的基本思想如下乘数被划分为一系列三位子串,每个子串分别与相邻的子串有一位重叠,而第一个子串是由乘数的最低两位和组成。编码器则根据这些子串的内容产生编码以指导部分积的生成。

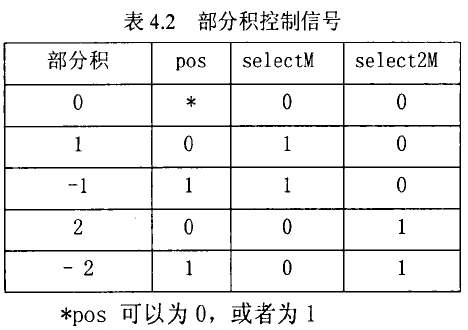

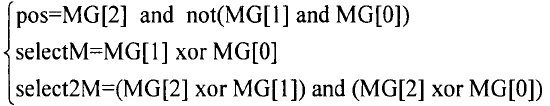

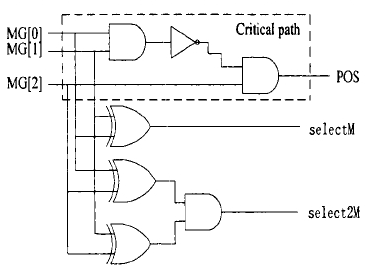

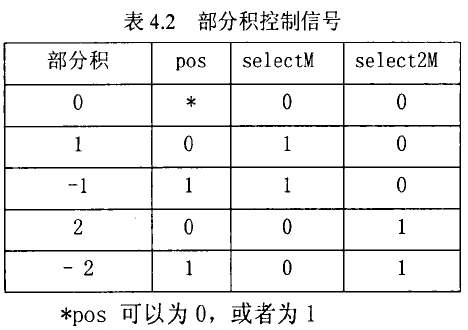

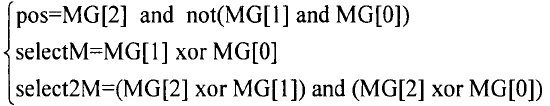

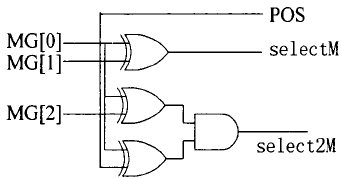

用三个控制位来表达这些信息。其中 selectM 为 1 表示部分积的绝对值是被乘数绝对值的 1 倍, select2M 为 1 为表示部分积的绝对值是被乘数绝对值的 2 倍,pos 为 0 表示部分积的符号与被乘数的相同,为 1 则表示部分积的符号与被乘数的相反。

控制逻辑:可以看出,selectM 和 select2M 需要两个门延迟就能得到,而 pos 需要 3 个门延迟,是关键路径。同时,此关键路径的实现需要两个与门和一个反向器,面积开销较大。

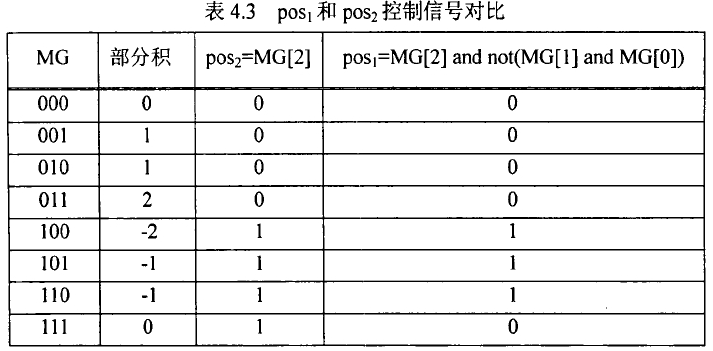

通过伪 1 变换减少 BOOTH 算法延迟

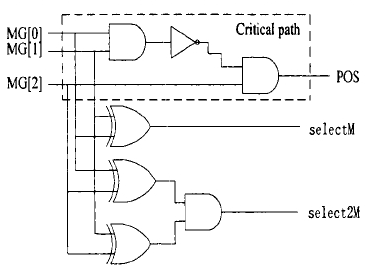

当部分积为 0 (MG = 000 | 111)时,pos 可为 1 也可为 0 。直接用 MG[2] 表示 pos (定义为pos2),可以看出仅当 MG 为 111 时 pos2 != pos1 ,但此时部分积 为 0 ,并不产生影响。

所以可以直接用直接用 MG[2] 表示 pos ,简化逻辑:

舍入

就近舍入 RNE/RMM :舍入为最近可表示的数

多余位的值超出规定的最低有效位值 LSB 的一半,则应向最低有效位进 1,否则简单的截尾即可。对于恰好是的一半值的这种特殊情况,要根据当前的值来分别讨论若 LSB 现为 0 ,则简单的截尾;若 LSB 现为 1 ,则向 LSB 进1。

朝 0 方向舍入 RTZ:截取所需位数,舍弃后面所有位

简单地截尾。

朝 $-\infty$ 舍入 RDN :总是取左边最近可表示数

对正数来说,直接截尾。

对负数来说,多余位全为 0 则直接截尾,不全为 0 则向 LSB 进 1。

朝 $+\infty$ 舍入 RUP :总是取右边最近可表示数

对正数来说,多余位全为 0 则直接截尾,不全为 0 则向 LSB 进 1 。

对负数来说,直接截尾。