仿真与综合电路行为的不匹配

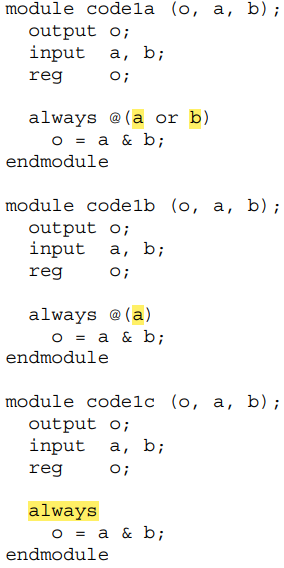

always 敏感列表

不完整的敏感列表

综合仍会推断出正确的电路(与门),但仿真行为与综合电路不符。

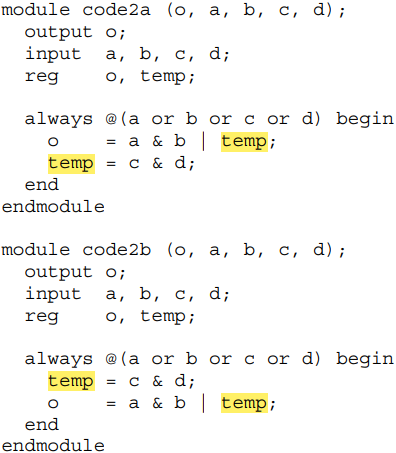

完整的敏感列表,但赋值顺序错误

综合仍会推断出正确的电路(与或门),但仿真行为与综合电路不符。

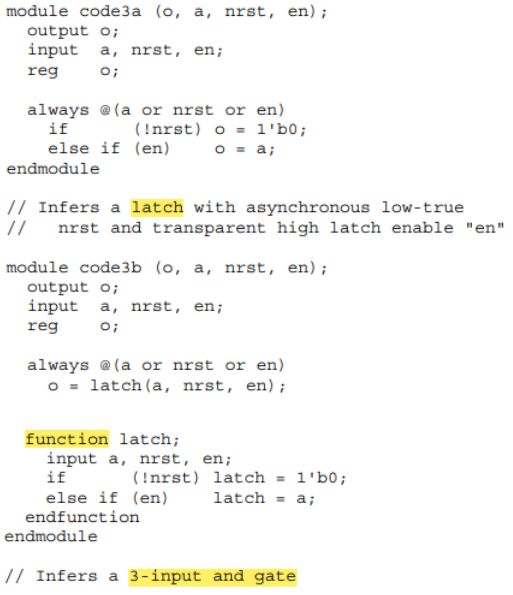

函数

函数会被综合为位组合逻辑,而如果函数中的代码对应锁存器,则综合前仿真视为锁存器,综合后仿真却视为组合逻辑,出现不匹配。

Case

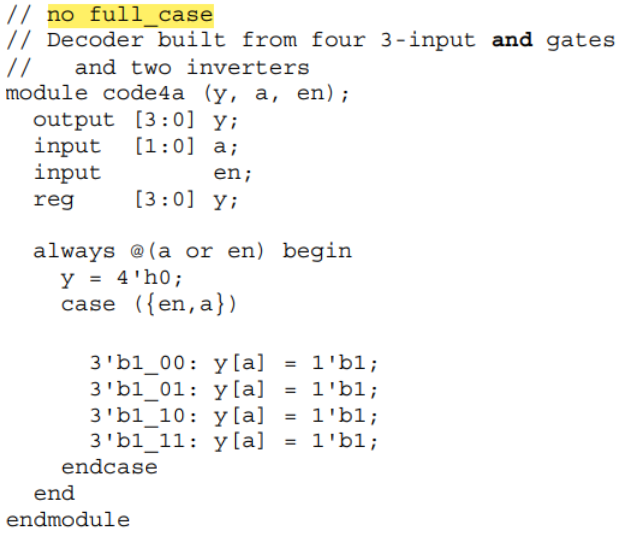

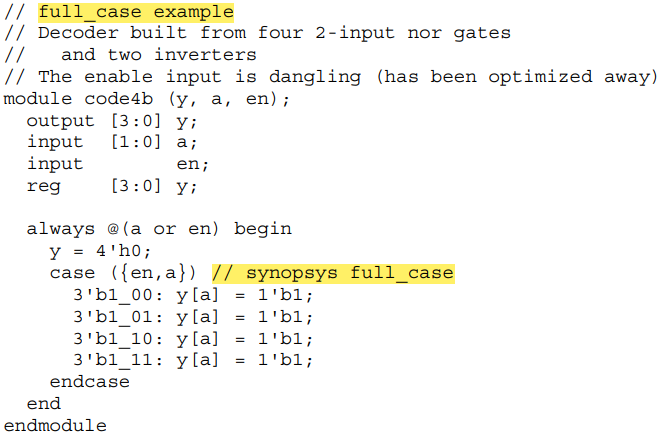

Full Case

// synopsys full_case 表示所有可能的 case 都已经列出,未列出的都是“不关心”的。

- 推导出 4 个 3 输入与门。

- 推导出 4 个 2 输入与门,

en信号被优化掉了。

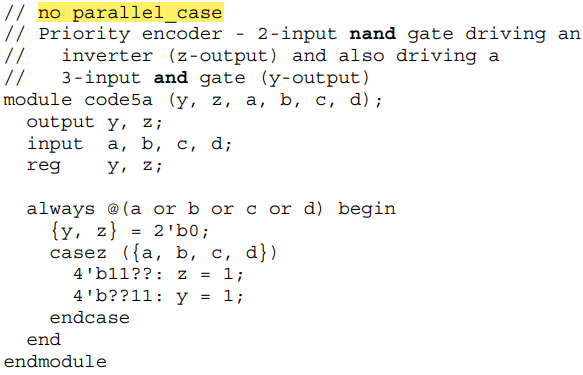

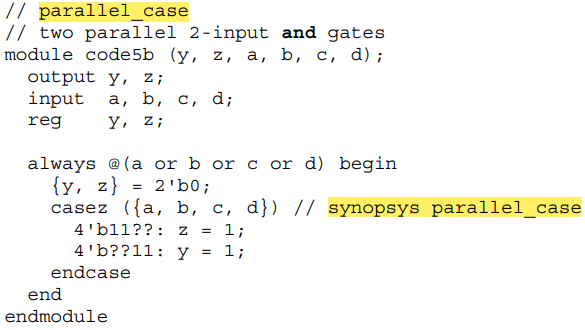

Parallel Case

// synopsys parallel_case 告诉综合工具应并行检验所有条件,即使存在重叠的条件。

重叠的条件平常会推导出优先级编码器,但在 parallel case 中会推导为无优先级。

z的 case 条件优先级高于y,所以y的条件中必须排除与z重叠的部分,推导出优先级。

- 在

parallel case中,各个条件无优先级,故各自z和y各自推导出 2 输入与门。

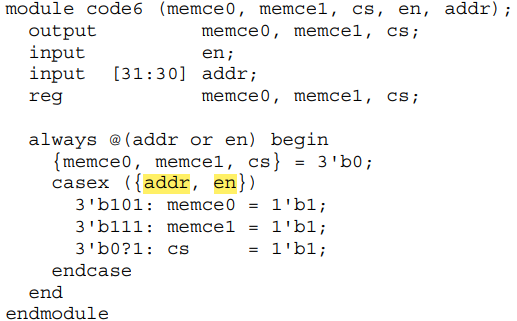

casex

casex 将 x 态视作不关心。当信号被初始化为未知状态时,可能会导致 x 态传播,但 casex 不能检测到这样的问题。

- 当

en因为某种原因变为x态,casex仍会根据addr进行匹配、执行,掩盖了x态的问题。addr也是一样。

- 不要使用

casex,最好使用casez。

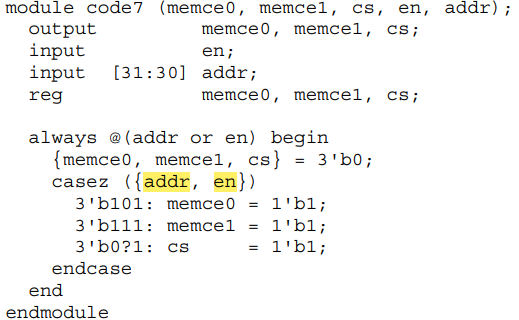

casez

casez 将 z 态视作不关心,可能会导致 casex 一样的问题。

- 但是用

casez于建模地址解码器和优先级编码器时非常有用,可以用?去匹配。

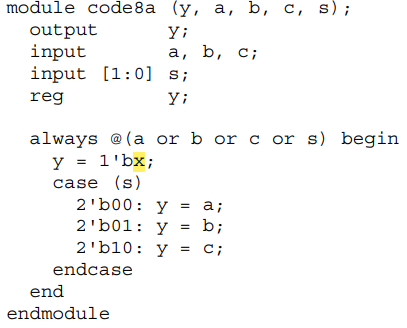

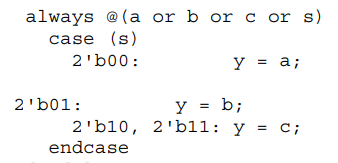

初始化

赋值 x 初始化

x 对于verilog仿真器是未知,对于综合工具是不关心(利于综合优化)。

- 赋值

x可能导致仿真综合不匹配,但是在 FSM 设计中可能有用,可以在仿真时检测错误的状态转换。 s == 2'b11时产生不匹配,但是若2'b11是不期望达到的状态,可以用于仿真调试。

- 这种方法可以综合成更小、更快的设计。

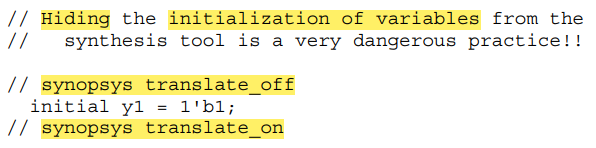

使用 translate_on/translate_off 初始化

?

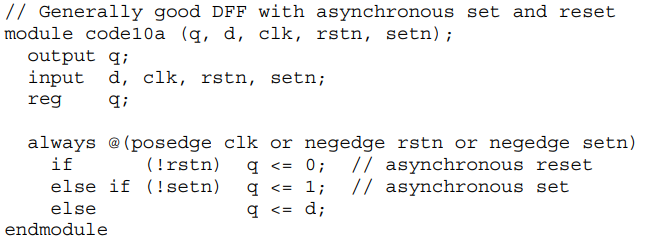

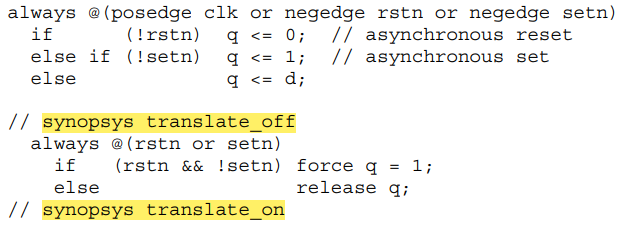

DFF:translate_on/translate_off 的一般用法

translate_on/translate_off在打印信息的时候很有用,但用于建模功能却很危险。- 一个例外是带异步复位和置位功能的 DFF ,典型的编码风格可以综合出正确的电路,并在 99% 的时间中仿真正确。

- 但是,当

rstn和setn都拉低后,rstn再拉高,此时q却未被置位。需要使用不可综合的构造才能完全与综合后的电路行为 100% 匹配。

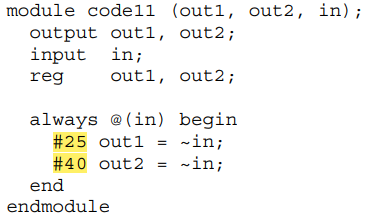

延时

在赋值左侧设置延时可能导致仿真与综合电路行为不匹配。

- 当

in发生改变,经过 65 个时间单位才退出always块,期间in再次发生改变也不会再次进入always块,计时期间其他事件都被忽略。这显然与综合后电路的行为不符。