复位

- 对于单个 ASIC 而言,复位的主要目的是强制 ASIC 设计(RTL 等)进入已知状态,以进行仿真。

- ASIC 制作完后,是否需要复位由一些因素决定。如果设计得当,使所有未知状态都指向合法初始状态,则不需要复位

- 如果 ASIC 中的状态机在综合时利用了

don't care优化,则需要复位。

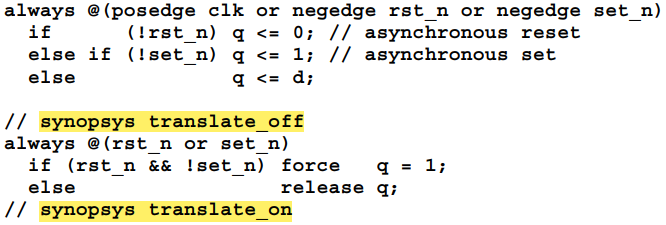

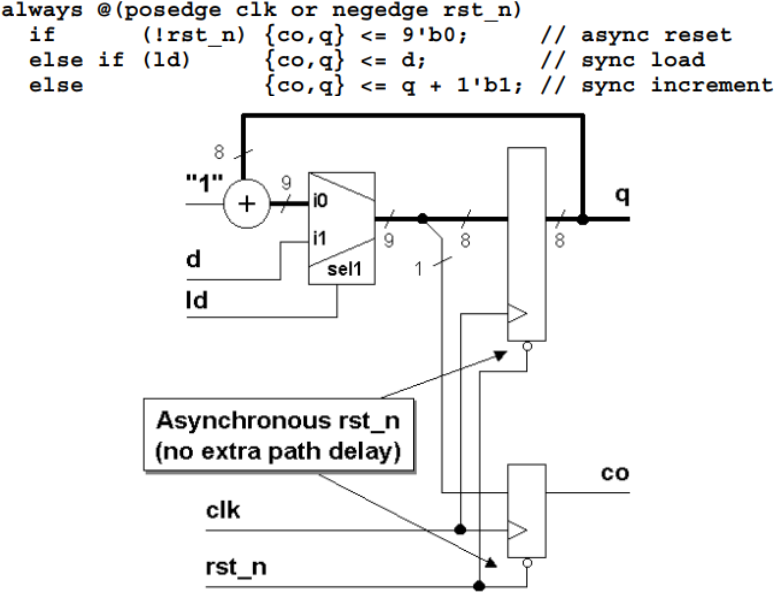

带复位触发器的建模

- 一个给定功能的所有触发器都应该在一个过程块中建模,例外是下述的同步触发器 & 无复位跟随器。

- 触发器的

always块中都应用非阻塞赋值<=。

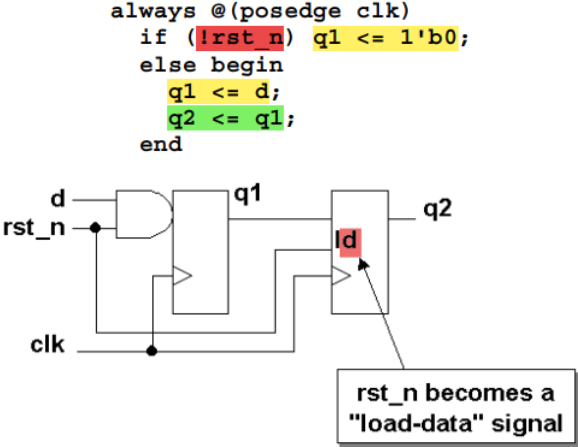

同一个 always 中建模不同类型的触发器

- 错误:在一个

always中混合建模同步复位触发器和跟随触发器,导致rst_n被推导为跟随触发器的使能信号ld。

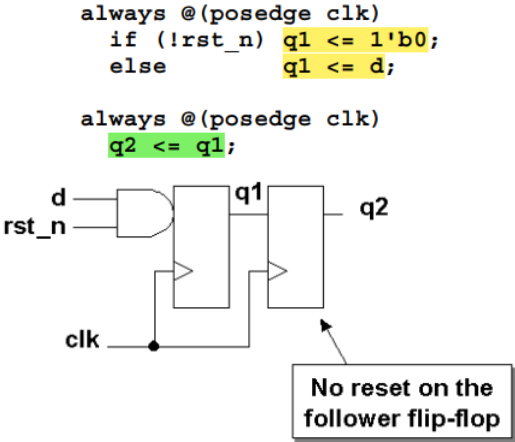

- 正确:分别在两个

always中描述。

- 不过,如果是异步复位,则会推导出相同的电路。

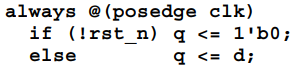

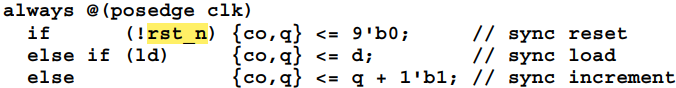

同步复位

编码风格

综合电路

- (#1)触发器无同步复位端口,复位信号为

d输入逻辑云的一部分。- 复位树扇出高,相对于时钟而言可能是一个晚到信号,所以尽量限制复位信号到

d之间必须穿越的逻辑。 sync_set_reset可以帮助推导这种触发器,但是需要注意前后仿不一致的问题。(?)

- 复位树扇出高,相对于时钟而言可能是一个晚到信号,所以尽量限制复位信号到

- (#2)触发器有同步复位端口,复位信号直接接入。

优点

- 可以过滤复位毛刺。但如果毛刺发生在时钟边沿附近,会导致亚稳态。

- 确保电路 100% 同步。

- 面积更小,但可能不明显。

- 对于基于周期的仿真器,效率更高。

- 在某些设计中,复位必须由一组内部条件产生,此时建议用同步复位,可以过滤时钟之间的逻辑等式故障。(?)

- 通过使用同步复位和多个时钟作为复位过程的一部分,可以在复位缓冲树内使用触发器,帮助缓冲树的时序保持在一个周期内。(?)

缺点

- 可能需要脉冲拉伸器,以保证复位脉冲足够宽,保证被时钟边沿采样。

- 仿真器阻塞。(?)

- 为了防止上电时三态总线上的总线争用,必须要有异步复位功能。

异步复位

异步复位最大的问题在于复位释放。

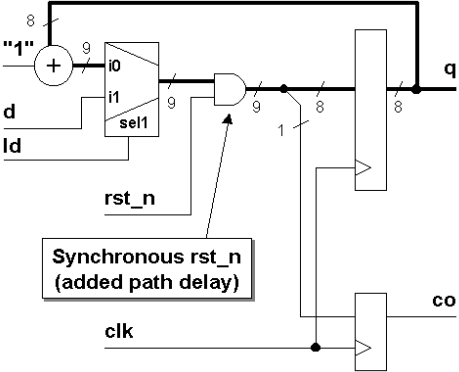

编码风格

Synopsys 要求,如果敏感列表中有任一个信号是边沿敏感的,则所有信号都必须是边沿敏感的。

时序约束

复位缓冲树?

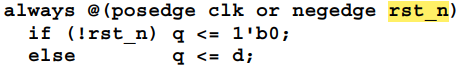

同时具有异步复位和异步置位功能的触发器

- 当

rst_n和set_n都拉低后,rst_n再拉高,此时q却未被置位:仿真与综合电路行为不匹配。 - 需要使用

synopsys translate_off/on和不可综合的构造才能与综合后的电路行为 100% 匹配。

优点

- 只要器件库有异步复位的触发器,就能保证数据通路是干净的,不会综合出额外的逻辑。

- 那些对数据通路时序要求极高的设计,无法接受因同步复位(#1)而在数据通路中插入额外的逻辑、增加额外的延时。

- 不过如果器件库也有同步复位的触发器,并且设计人员让 Synopsys 能实际使用这些端口,则不成立。

- 电路可以在有时钟和没时钟的情况下复位。

缺点

- 异步复位如果在有效时钟沿释放,会导致亚稳态问题。

- 电路板上的噪声或故障或系统复位可能造成假复位。(?)

- 使用异步复位的设计很难进行静态时序分析 STA ,必须对同步和异步复位的复位树进行时序分析,以确保在一个时钟周期内释放复位。复位树的时序分析必须在布局后进行,以确保这一时序要求。(?)

- 对于 DFT ,如果异步复位不是由 I/O 引脚直接驱动,则在 DFT 扫描和测试时必须禁用来自复位驱动的复位网。(?)

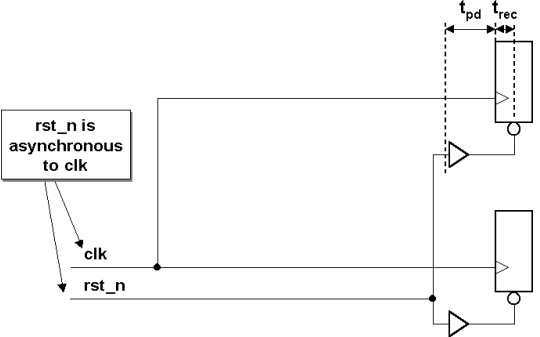

异步复位问题

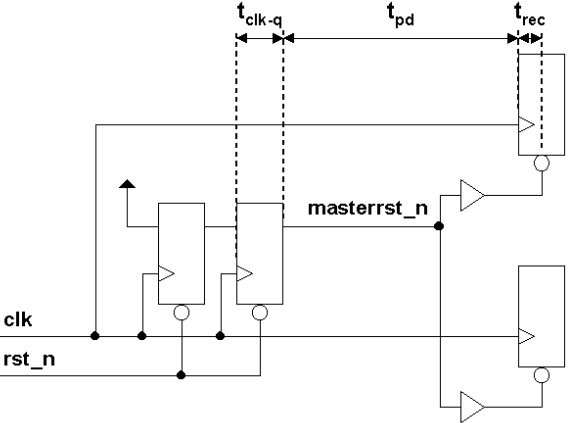

复位恢复时间 trec

- 复位恢复时间指从复位释放到下一个时钟有效边沿之间的时间,需要满足建立时间tsu,否则会导致亚稳态或信号完整性的问题。

- Verilog 2001 有三个内指命令用于模拟和测试恢复时间和信号移除时序检查:

$recovery$removal$recrem

复位去除时间

跨越不同时钟周期的复位释放

由于复位信号到达不同触发器时间存在偏差,可能导致两个触发器在不同的时钟周期释放复位。

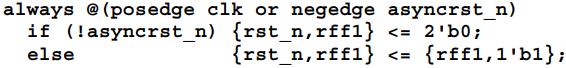

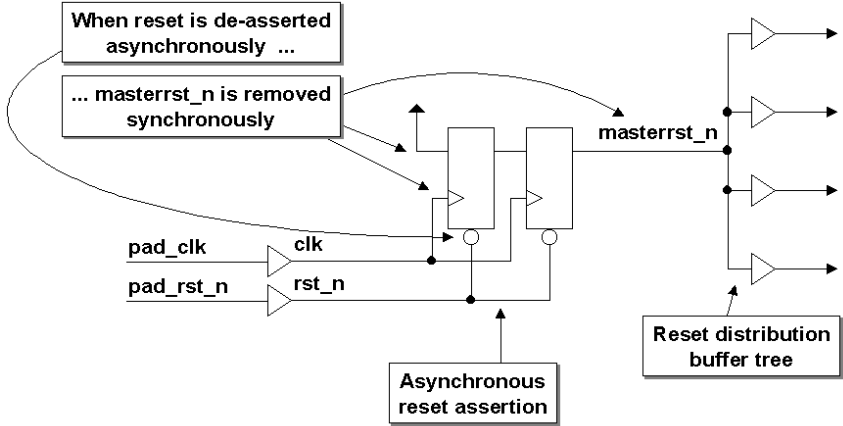

复位信号同步电路

每个使用异步复位的 ASIC 都应该包括一个复位信号同步电路。

- 第二个触发器用于消除复位释放靠近时钟边沿导致的亚稳态。

- 同步复位信号经过 clk-q 延时、复位分配树延时到达,还需要满足目标触发器的复位恢复时间。(T < tclk-q + tpd + trec + tsu?)

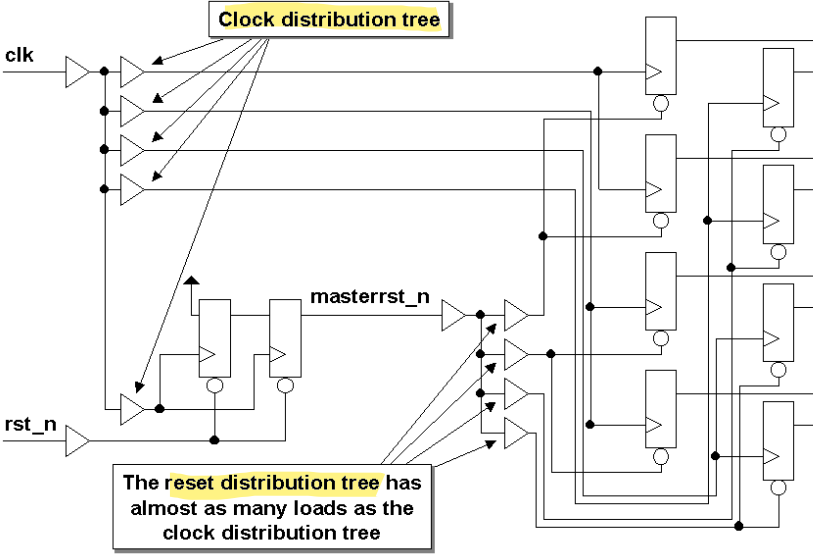

复位分配树

- 复位树通常具有和时钟树一样多的负载。

复位信号的偏移(skew)

- 复位树与时钟树的区别是偏移(skew)的平衡。

- 与时钟信号不同,只要复位信号的延时足够短,能够在一个时钟周期内传播到所有复位负载,并仍满足目标触发器的复位恢复时间要求,那么复位信号之间的偏移(skew)就无关紧要。

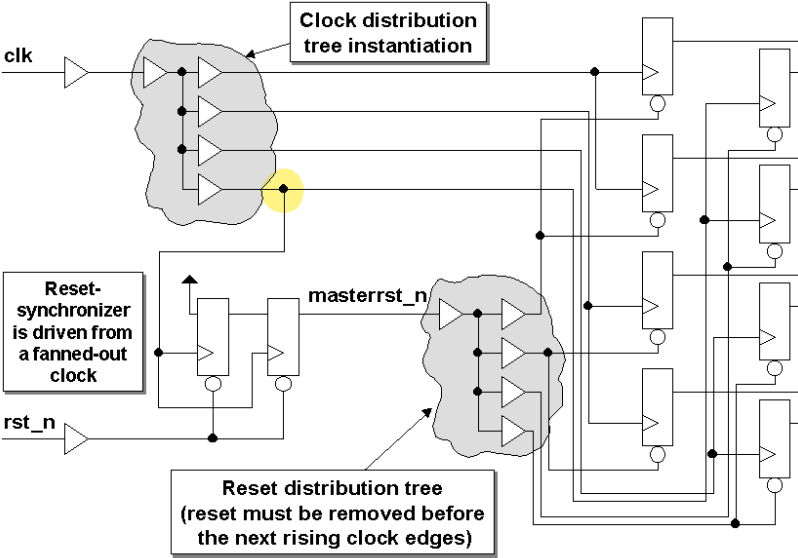

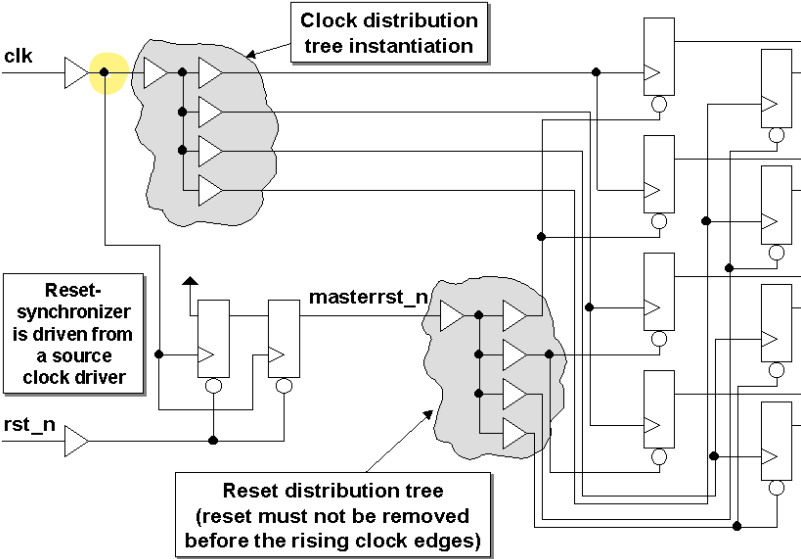

复位树和时钟树的时序(复位同步电路的时钟来源)

必须根据 clk-q 复位树的时序分析时钟树时序。

- 为复位树提供时钟的最安全方法是:时钟树的叶时钟为复位同步触发器提供时钟。

- 但是大多情况下,一个时钟周期不够时钟脉冲穿过时钟树、复位信号穿过 clk-q 、再穿越复位树。

- 为了加快复位到达所有目标触发器的速度,复位同步触发器采用时钟树中更早的时钟。

- 在完成布局并获得两棵树的实际时序之前,无法进行详细时序调整。

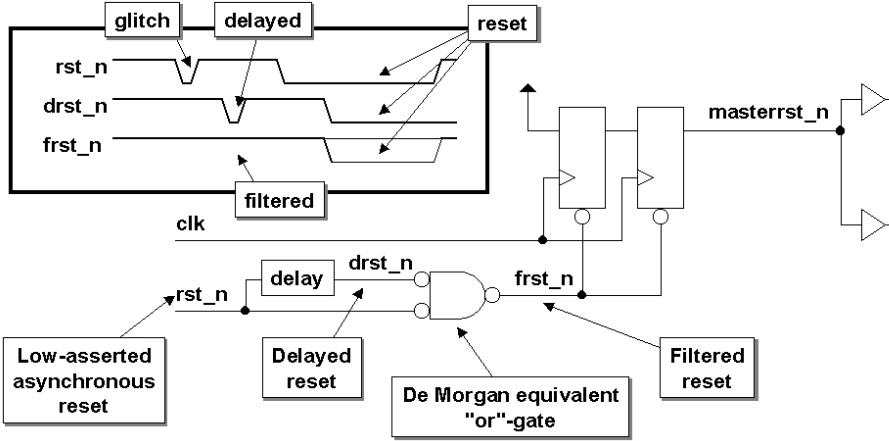

复位毛刺的过滤

- 这种方法可以过滤复位毛刺,但它是 ugly 的。(?)

- 需要一个数字延迟(随温度、电压等变化)

- 复位输入 pad 应该是施密特触发 pad 。

- 一些供应商还提供了可实例化的延迟硬件宏。

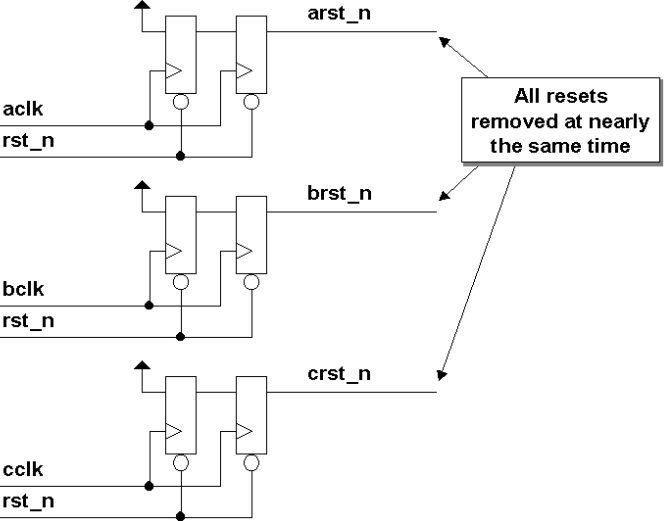

多时钟域复位

对于多时钟设计,每个时钟域都应该使用单独的复位同步电路和复位分配树,保证满足复位恢复时间。

无协调复位释放

- 对于许多多时钟设计,各时钟域的复位时间之间没有联系。

- 只需各自创建独立的复位同步电路就行。

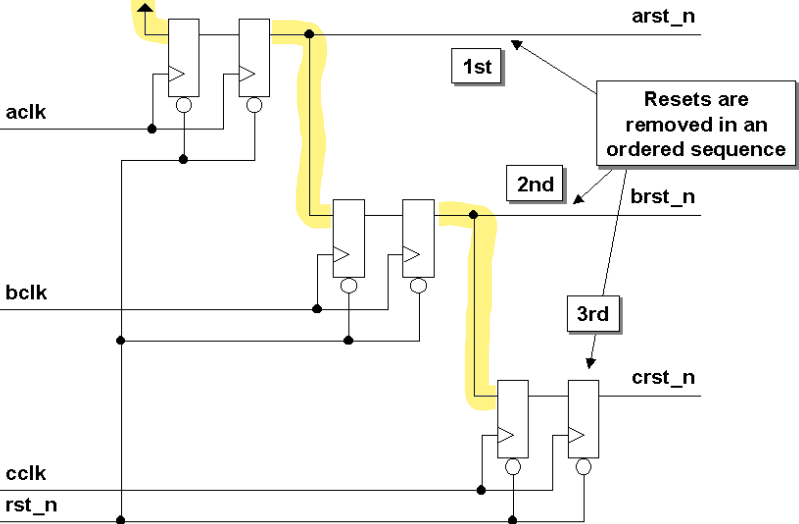

有序复位释放

- 对于某些多时钟设计,必须按照正确的顺序释放复位。

- 将各个复位同步电路进行 d-q 级连,实现顺序释放。

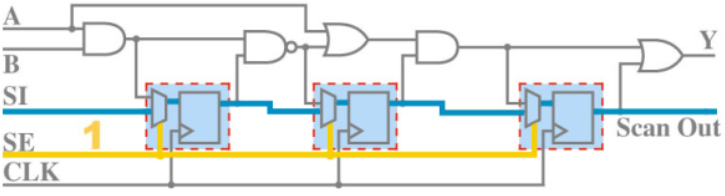

异步复位与 DFT

DFT

- 扫描链插入:将触发器换成扫描触发器,并将它们拼接成扫描链。

- ATPG:程序生成扫描向量。

- 测试:

- 扫描移位模式,将测试向量扫描到所有触发器中。

- 从扫描移位模式切换到功能数据输入模式。

- 经过一个功能时钟。

- 切换回扫描移位模式,扫描出结果,同时扫描入下一个测试向量。

- DFT 通常需要两个控制引脚:

- 模式切换引脚

- 移位使能引脚

(?)

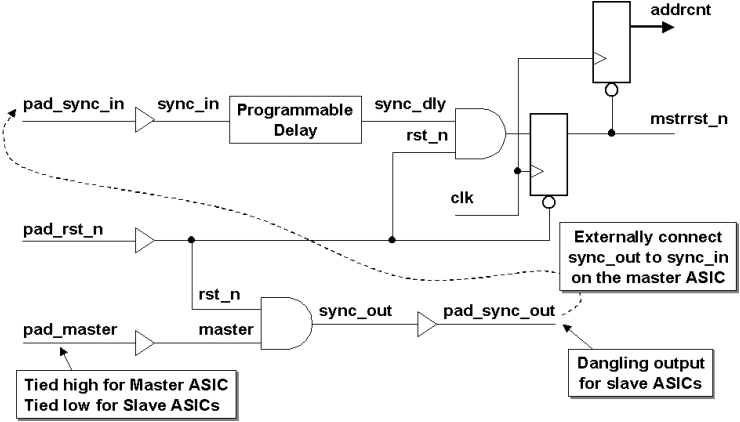

多 ASIC 复位同步

对于一些设计,多个 ASIC 需要准确地在同一时间进行复位释放。可能受板布局、工艺、温度影响。