NBA

竞争 Race Condition

- 根据 IEEE Verilog 标准,一些语句具有规定的执行顺序,另一些语句则没有规定的执行顺序。

- 当多个语句在相同的仿真时间点执行时,语句的执行顺序未知,可能产生不同的结果,即 Race Condition 。

Blocking or Nonblocking: Simulation

Guidelines:组合逻辑电路用阻塞赋值,时序逻辑电路用非阻塞赋值。

忽略上述准则仍然可以综合出正确的电路,但仿真可能与实际电路的行为不匹配。

阻塞赋值 Blocking Assignment

在不被任何其他 Verilog 语句中断的情况下,计算 RHS 并更新 LHS 。

当一个过程块中的 RHS 也是另一个过程块中的 LHS 时,并在同一个仿真时间执行,就会出现 Race Condition 。

非阻塞赋值 Nonblocking Assignment

- 计算 RHS

- 更新 LHS

非阻塞赋值并行执行。

非阻塞赋值仅用于 reg 类型,即只用于过程赋值块内。

Coding Guideline

- 对时序逻辑电路建模时,使用非阻塞赋值

<=配。 - 对锁存器建模时,使用非阻塞赋值

<=。 - 使用 always 块对组合逻辑电路建模时,使用阻塞赋值

=。 - 在同一个 always 块中混合建模组合逻辑和时序逻辑电路时,使用非阻塞赋值

<=。 - 不要在同一个 always 块中混合使用阻塞

=和非阻塞赋值<=。 - 不要在多个 always 块中对同一个变量赋值。

- 使用

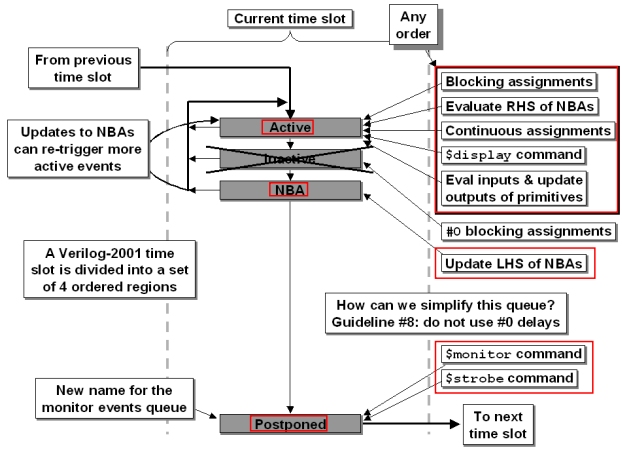

$strobe来打印非阻塞赋值<=的变量。 - 不要使用

#0。

Verilog 仿真的分层事件队列(Stratified Event Queue)

- Active

Inactive- NBA

- Monitor/Postponed

情况

自触发的 always 块(Self-triggering Always Block)

?

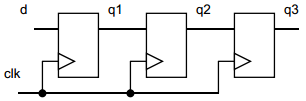

流水线建模(Pipeling Modeling)

1 个 always 块,阻塞赋值(需要仔细安排赋值顺序)多个 always 块,阻塞赋值(错误)- 1 个/多个 always 块,任意顺序的非阻塞赋值

触发器

1 | module dff( |

带反馈的时序逻辑电路建模(Sequential Feedback Modeling)

Linear Feedback Shift-Register (LFSR)

使用 <=

1 | s |

Combinational Logic: Blocking Assignment

Mixed Sequential & Combinational Logic: Nonblocking Assignment

(X) Mixed Blocking & Nonblocking Assignment

(X) Multiple Assignment to Same Variable

对于非阻塞赋值的一些错误认知(Common Nonblocking Myths)

(✗)在同一个 always 块中对同一个变量进行多次非阻塞赋值

<=是未定义的行为(✓)最后一个赋值语句胜出

(✗)

$display()对于非阻塞赋值的变量无效(✓)非阻塞赋值在

$display()之后生效,用$strobe(✗)

#0语句在每个 time step 的最后生效(✓)

#0语句在每个 time step 的 Inactive 阶段生效