FSM

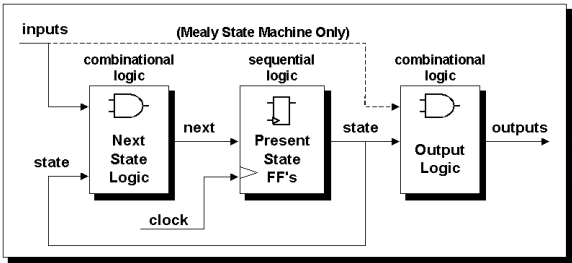

Moore & Mealy FSM

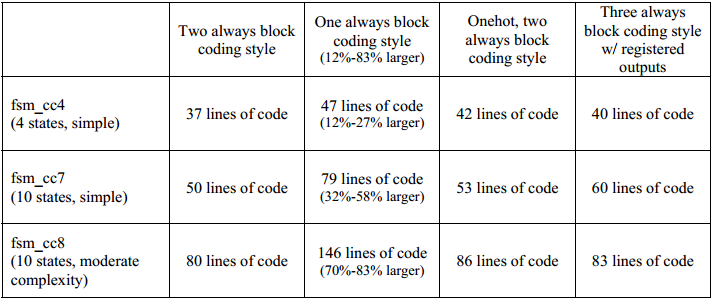

整体风格

1-always (X)

x

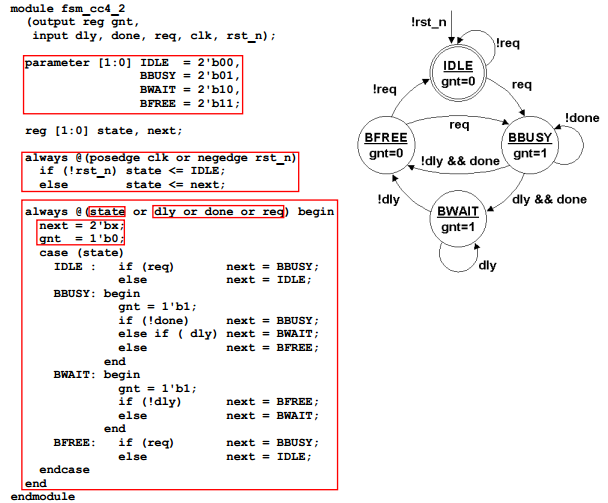

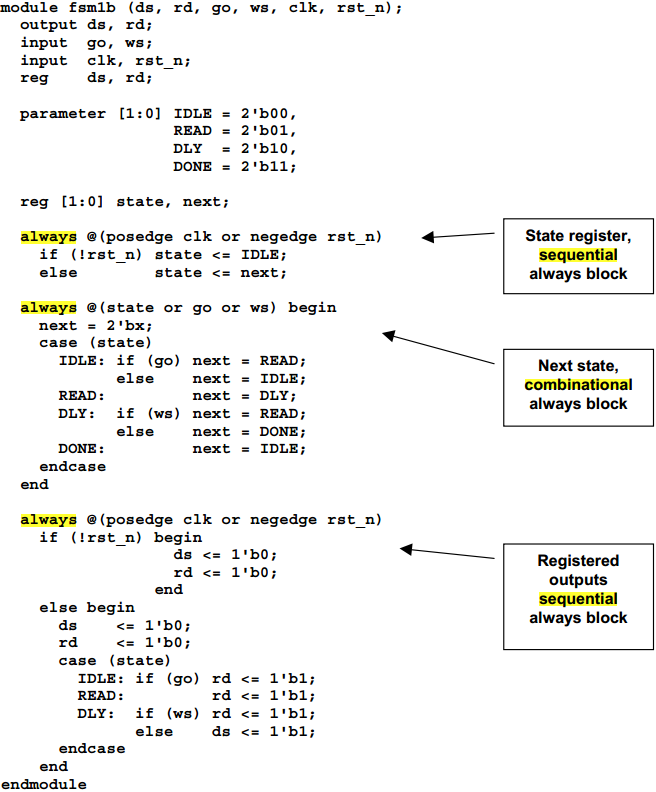

2-always

- sequential state register

- combinational next-state & combinational output logic

Coding Style Notes:

- Parameters instead of the Verilog `define macro definition are used to define state encodings.

- Combinational always block sensitivity list is sensitive to changes on the state variable and all of the inputs.

- Combinational always block has a default next state assignment at the top of the always block (X to debug, or IDLE, or just set to the value of the state register).

- Default output assignments are made before coding the case statement (this eliminates latches ,reduces the amount of code required, highlights in the case statement exactly in which states the individual output change).

- There is an if-statement, an else-if-statement or an else statement for each transition arc in the FSM state diagram.

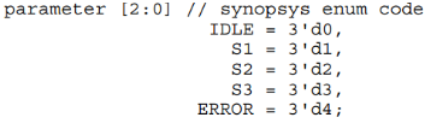

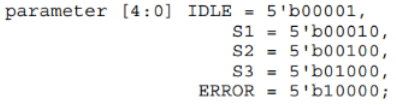

状态编码

二进制编码

- 需要的 FF 少,但是组合逻辑多。

onehot 编码

- 需要的 FF 多(无所谓),但是组合逻辑可以得到优化(速度快)。

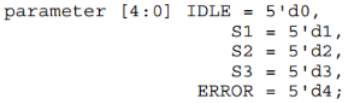

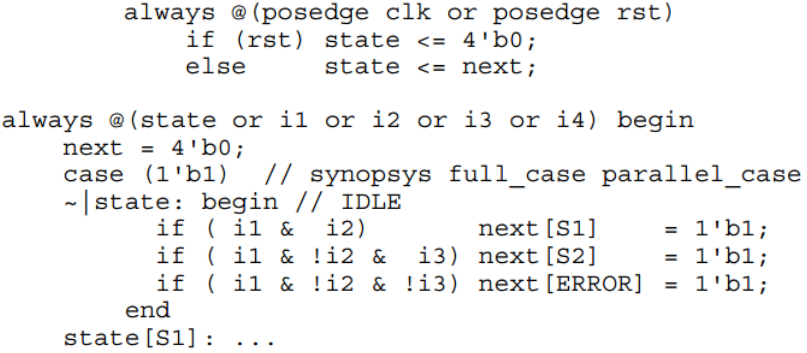

简化 onehot 编码

parameter 代表的不是编码(encode),而是对寄存器相应 bit 的索引(index)。

零空闲 onehot 编码

- 将 ERROR 或 IDLE 编码设为 0 。

- 重置时将 state 置为全 0 ,再设置相应位。

输出生成

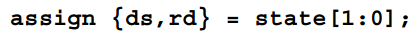

输出为组合逻辑(2-always & assign)

- 输出可能有毛刺。

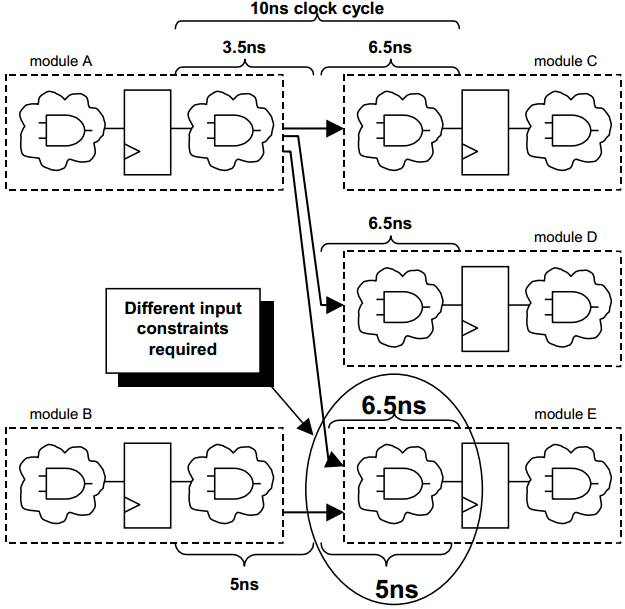

- 输出逻辑云消耗了下一级模块的可用时钟周期。

- 时序约束复杂。

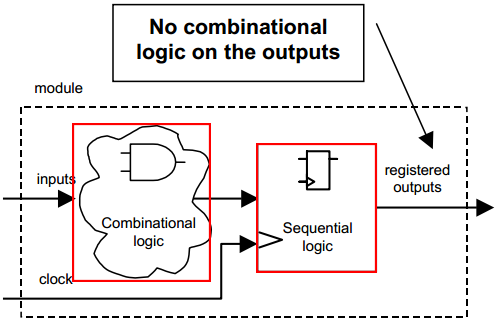

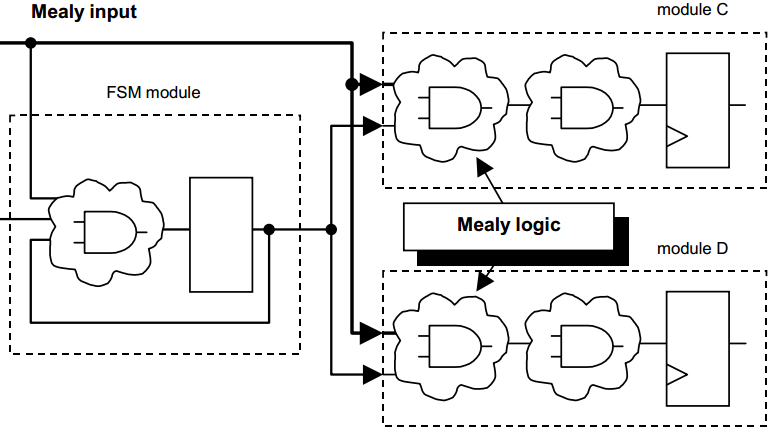

Moore 机同步输出

设计分区(cloud-register)

- 通过 FF 同步输出。

- 简化了综合时的时序约束任务。

3-always

(?)state & next_state

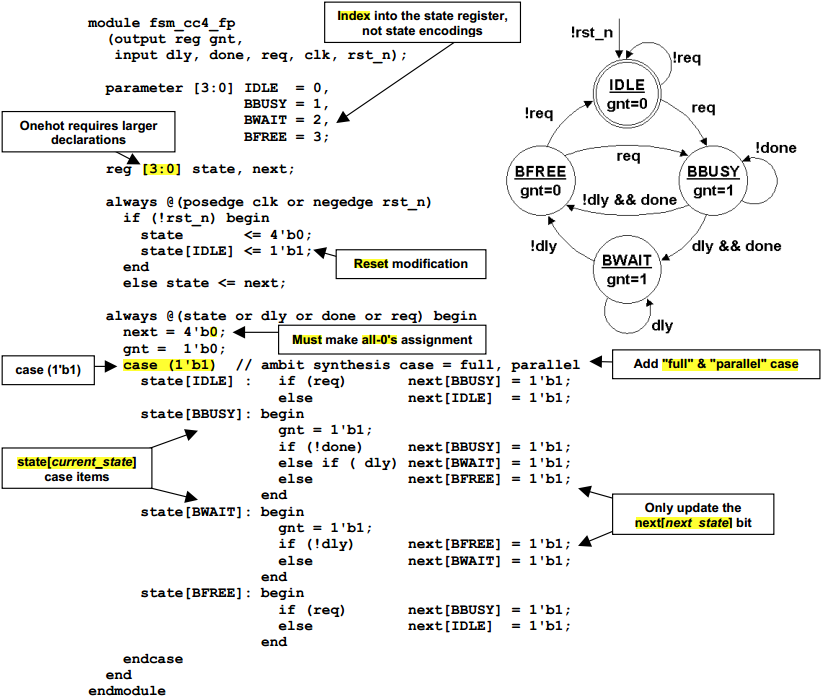

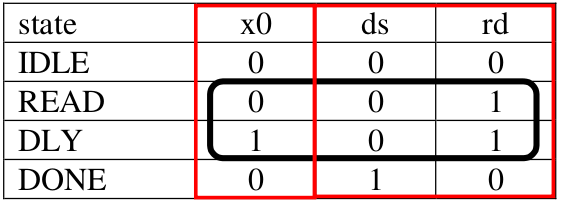

状态编码输出

- 输出即为状态编码的某些位,需要根据输出对状态编码进行设计。

- 将状态与输出列成表格。

- 发现有多个状态对应同一种输出,则需要添加 n 位状态编码,以消除状态编码重叠。

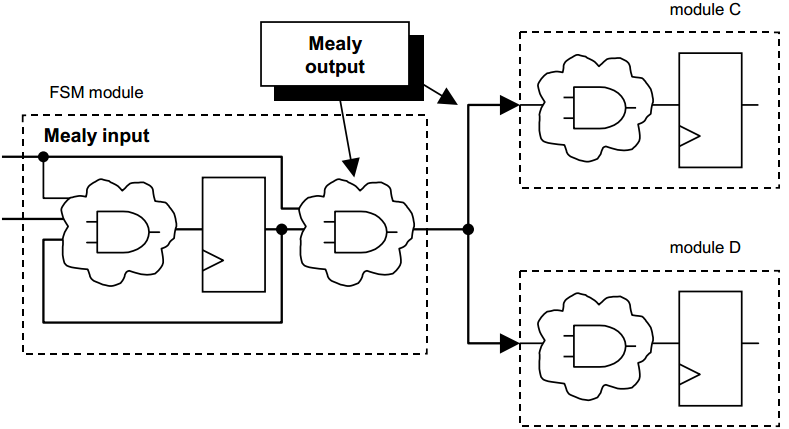

Mealy 机异步输出

通常可以将输出逻辑移到下一级的输入逻辑。

Synopsys FSM Tool

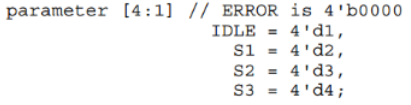

Full_case/ Parallel_case

?

state encode

?

对比