CDC

亚稳态 metastability

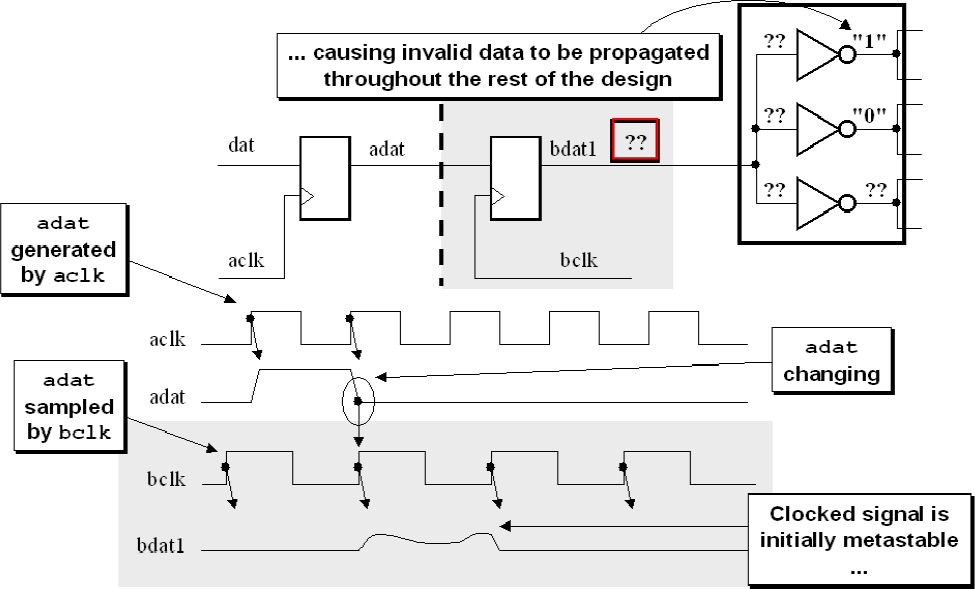

亚稳态:由于不满足建立/保持时间,触发器在时钟边沿采样到变化中的信号,触发器输出信号在一段时间内不处于稳定的 0/1 状态,经过一段稳定时间 tMET 后恢复正常(可能是 0 也可能是 1 )。

亚稳态不能完全避免。

亚稳态会穿越后续电路,导致非法信号值传播到整个设计的其余部分。

同步器 Synchronizer

两种同步场景

- 不需要采样每个值(允许漏采样),但是需要采样准确。(如 FIFO )

- CDC 信号必须被正确地接收,然后 CDC 信号才能变化。

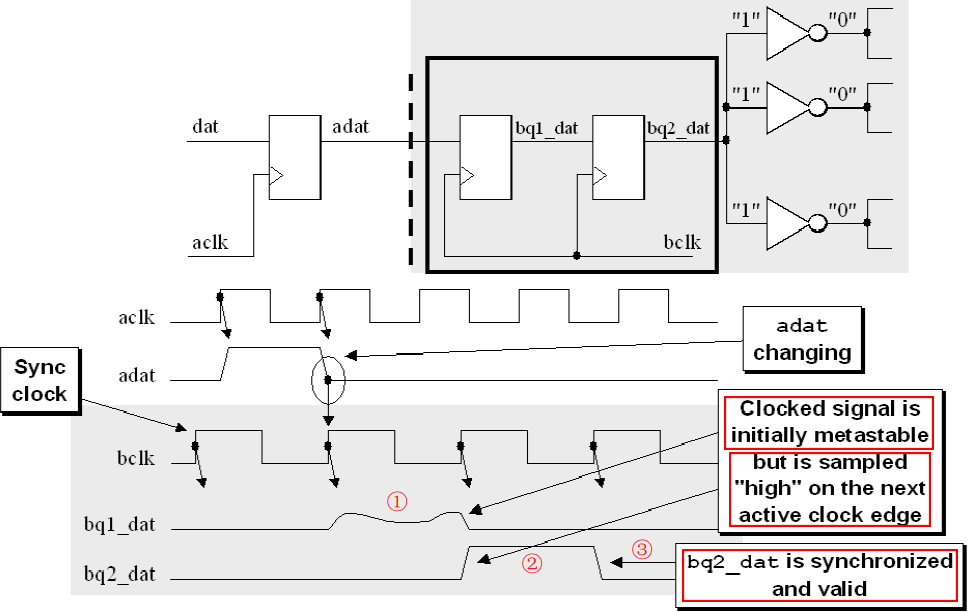

2 个触发器的同步器

- 第一级触发器将异步输入信号采样到新的时钟域,并等待一个时钟周期,使第一级输出信号上的亚稳态衰减。

- 第二级触发器采样,得到稳定有效的信号。

- 对于更高速的设计,亚稳态经过一个时钟周期仍然无法恢复,需要增加触发器数量,在后续几级内应恢复正常。

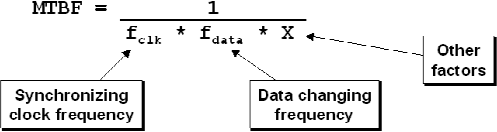

同步器的 MTBF

- 理论上,当第二级触发器采样时,第一级触发器输出可能仍处于亚稳态,导致第二级输出信号仍为亚稳态。

- MTBF 表示发生潜在故障之间的间隔时间。

- MTBF 随时钟频率和数据变化频率增加而减少,即故障发生的频率更高。

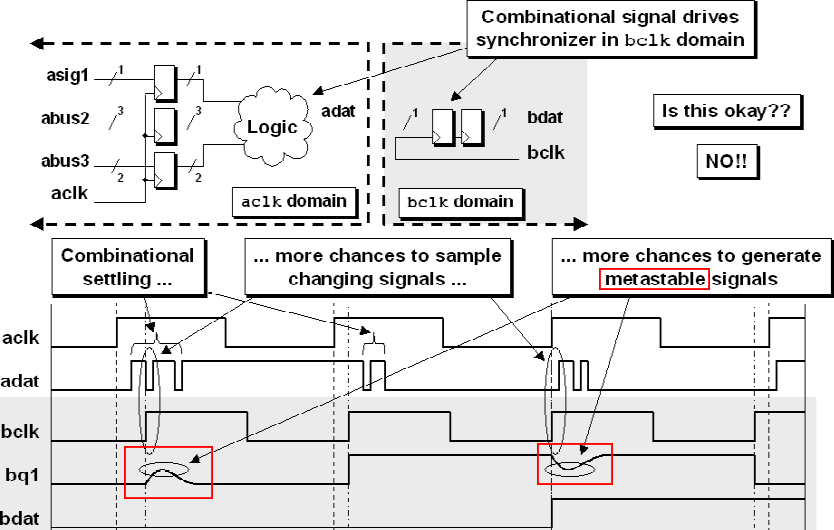

问题:在接收时钟域同步而不在发送时钟域同步?

将 CDC 信号在接收时钟域同步,是否就不需要在发送时钟域同步寄存?

- 答案是否定的。这会导致更容易采样到变化中的信号,导致亚稳态。

快/慢时钟域之间的信号传输

慢时钟 -> 快时钟

若快时钟的频率至少是慢时钟的 1.5 倍,则信号一定会被采样 1-2 次,不存在漏采样的问题。

快数据变化频率 -> 慢时钟域

- 来自发送时钟域的信号在被采样之前可能会变化两次,或者可能太接近较慢时钟域的采样边缘。

- 若不允许漏采样:

- 开环方法:不需要 acknowledge 信号

- 闭环方法:需要接收时钟域的 acknowledge 信号

三个边沿要求

- 对于 2 触发器同步器,CDC 信号保持稳定的时间至少是接收时钟域的 3 个时钟沿。(CDC 信号必须宽于接收域时钟的周期宽度的1-1/2倍)

问题

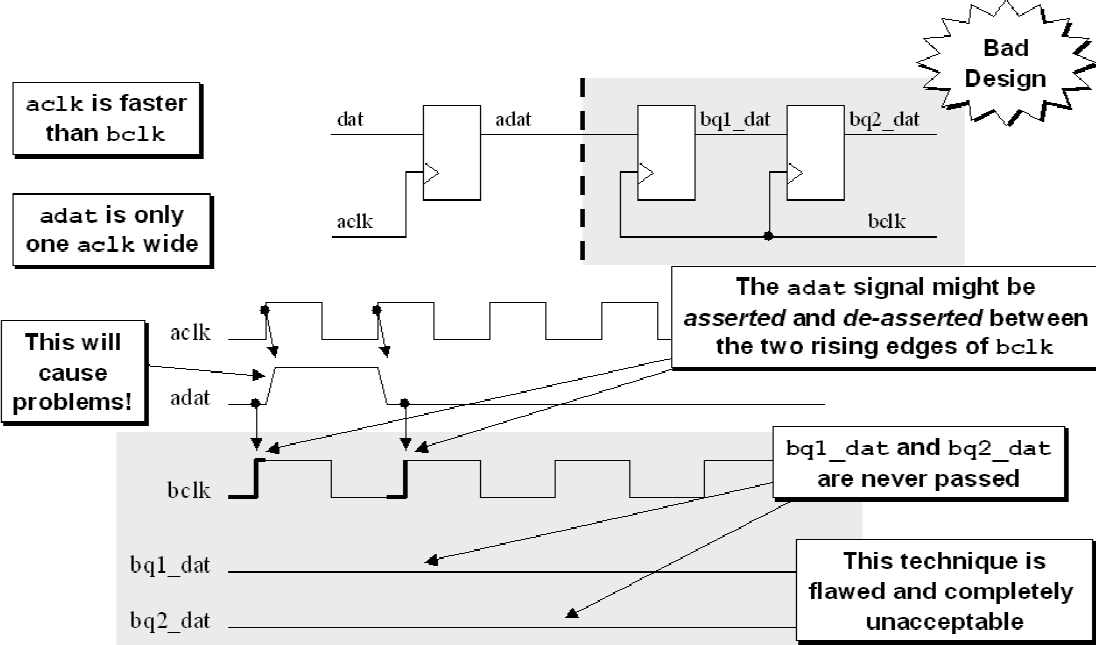

1 传输窄脉冲

当发送时钟域频率高于接收时钟域,且 CDC 信号脉宽仅为发送时钟域的一个周期:

- 可能漏采样。

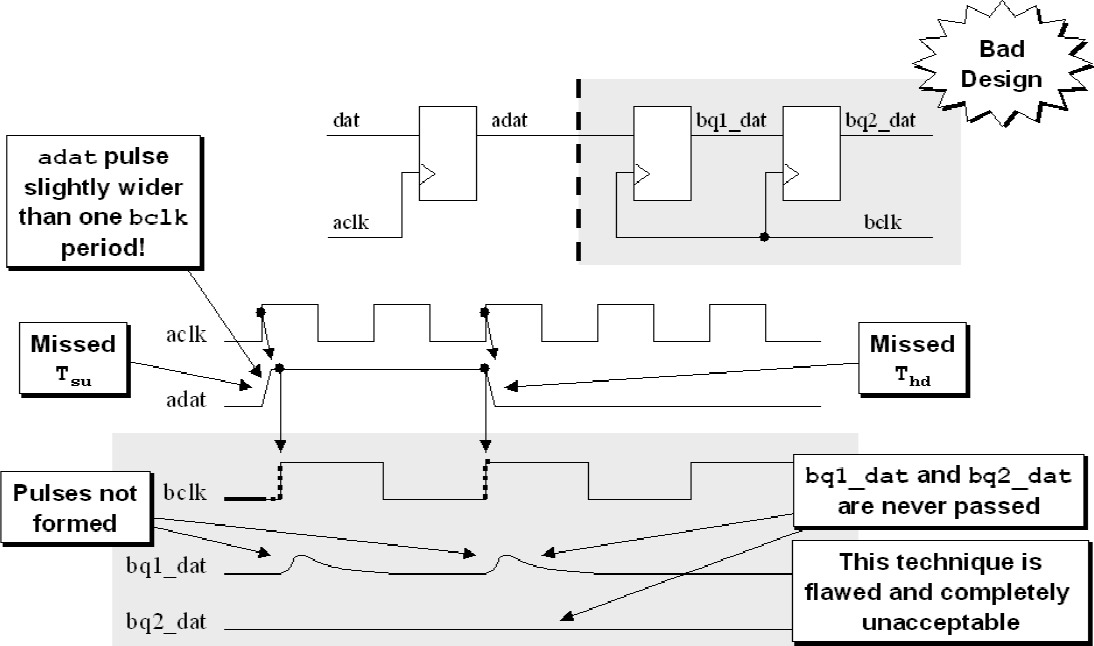

2 采样宽脉冲

当发送的脉冲宽度稍大于接收时钟周期:

- 可能脉冲上升沿和下降沿与接收时钟边沿太接近,不满足第一个时钟沿的建立时间、第二个时钟沿的保持时间,导致不能形成预期的输出。

解决方法

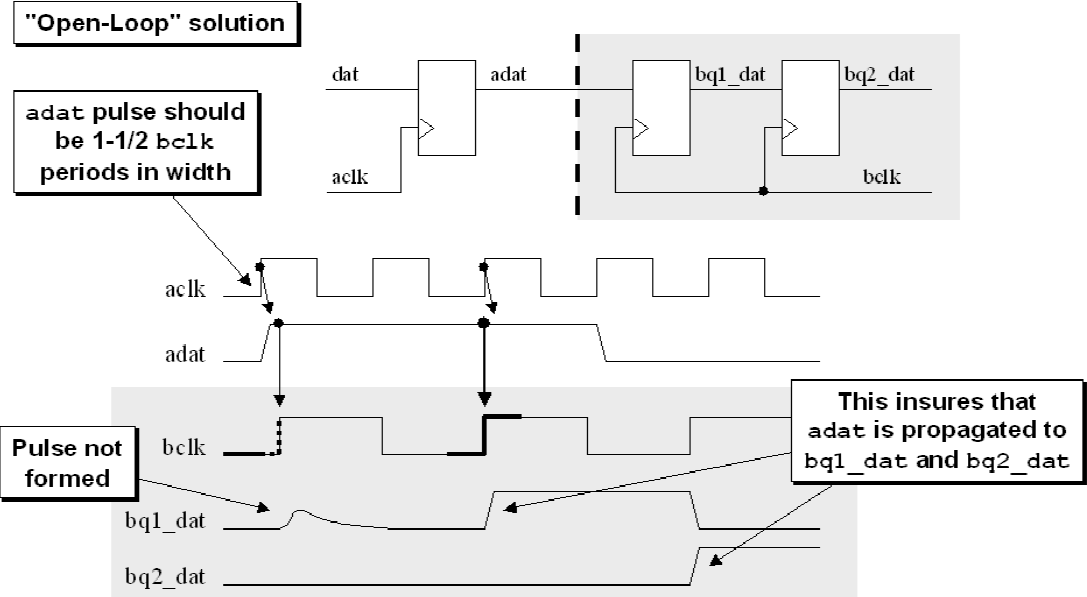

开环法

在超过采样时钟周期的一段时间内断言 CDC 信号,最小脉冲周期是采样时钟周期的 1.5 倍。

- 优点:不需要 acknowledge 信号,快。

- 缺点:设计要求变化时,需要重新分析。可用 SystemVerilog 断言检测输入脉冲是否未能超过“三个边沿”设计要求。

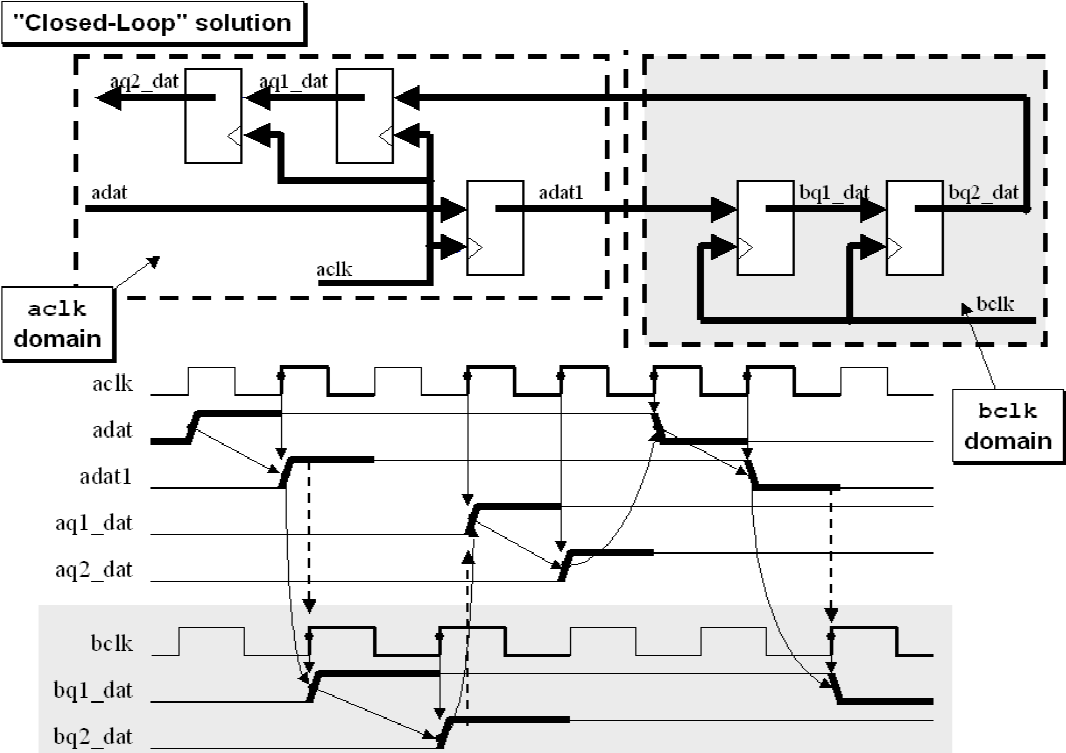

闭环法

将使能控制信号同步到接收时钟周期,再将确认信号同步回发送时钟周期。未收到确认信号之前,发送信号不能改变。

- 优点:安全。

- 缺点:在允许控制信号改变之前,在两个方向上同步信号可能导致相当大的延时。

多 bit CDC 信号传输

发送时钟域同步输出的多个信号会存在数据变化偏差(skew),可能导致接收时钟域不能同时采样到正确信号。

解决方法

- 多位信号整合

- 多周期路径

- 用格雷码传输

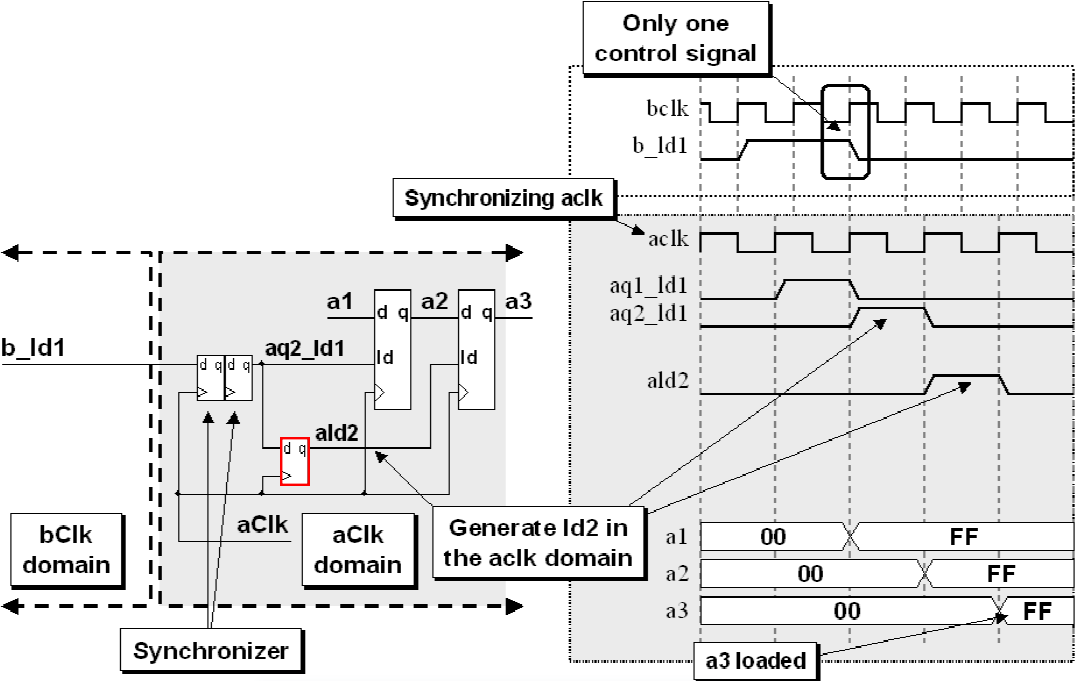

多位信号整合

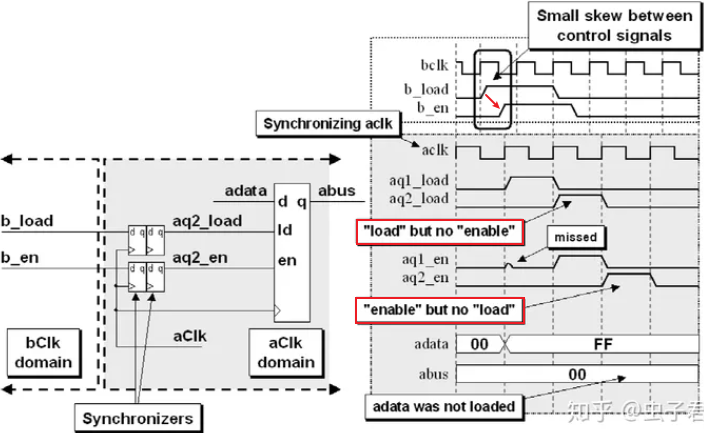

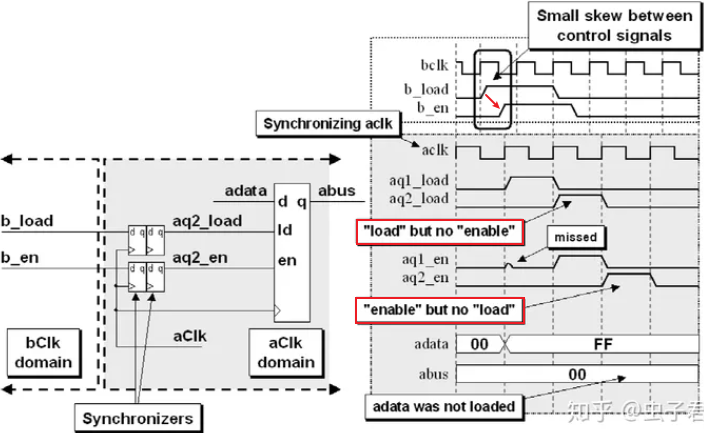

同时传递两个控制信号

两个控制信号存在小偏差,导致在接收时钟域的不同时钟沿被采样。

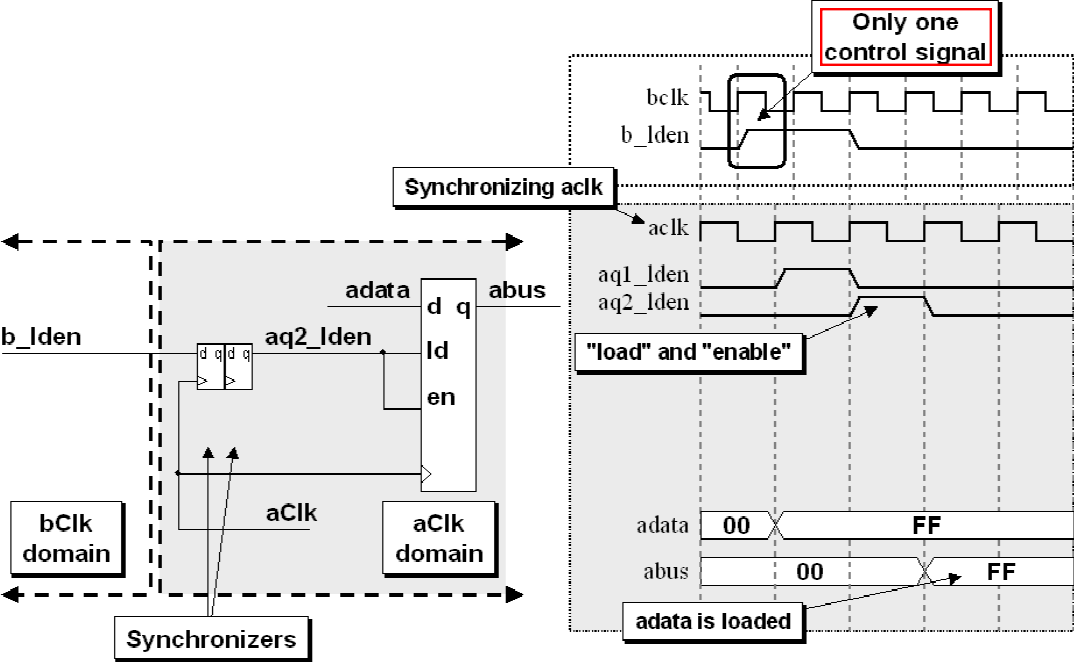

解决方法

将 en load 合并成 lden 信号。

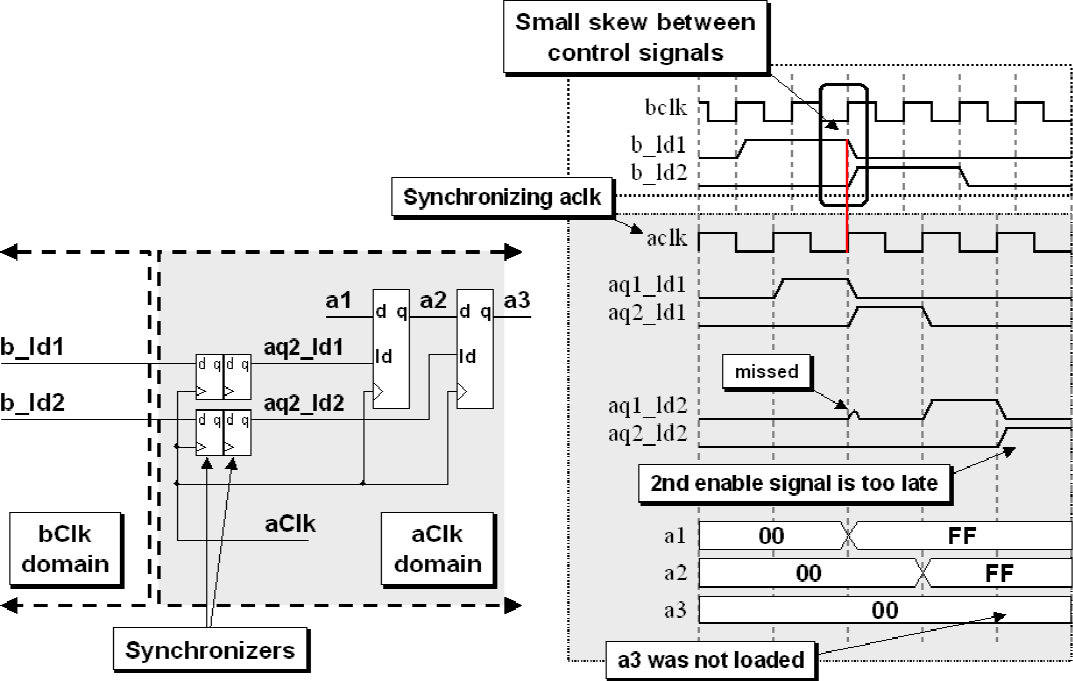

两个相移控制信号

接收时钟沿可能恰好在两个相移控制信号之间,导致在接收时钟域的使能控制信号链中形成单周期间隙。

解决方法

合并控制信号,在接收时钟域内生成第二相移流水线使能信号。

当必须要传输多 bit CDC 信号

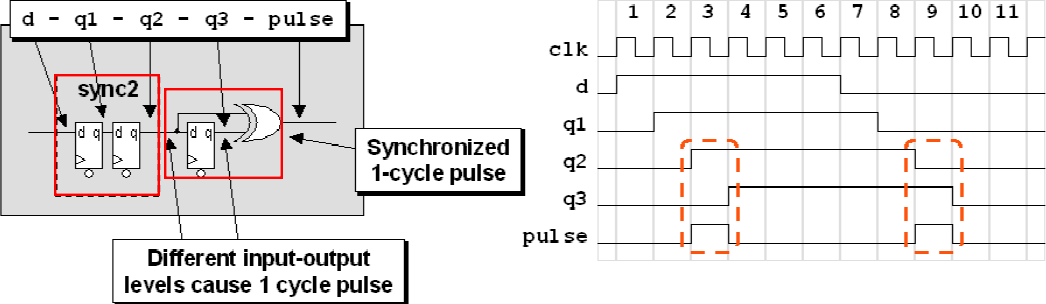

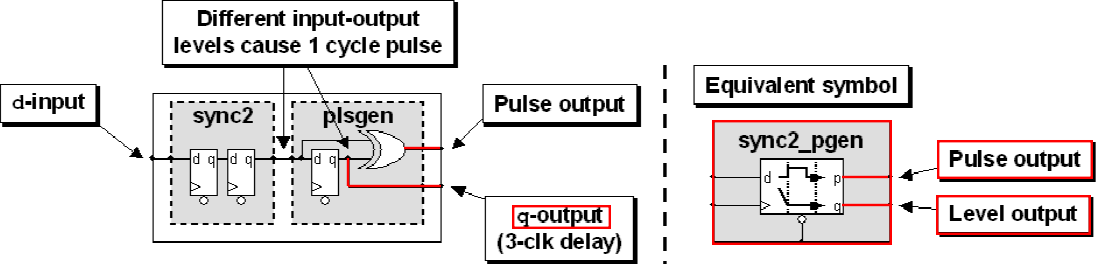

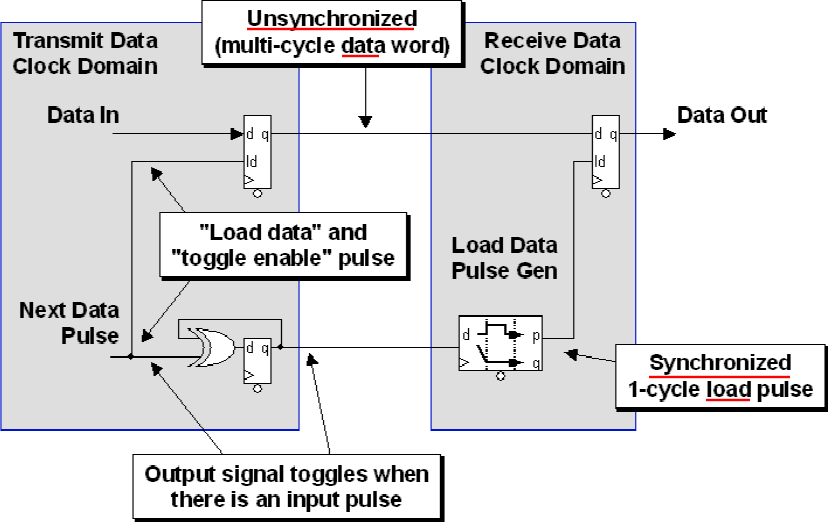

1 多周期路径 MCP

发送不同步的数据和同步的控制信号。

- 数据信号异步发送并保持稳定,在目标寄存器的输入上建立。

- 控制信号翻转,经过两个周期的同步,再通过一个脉冲发生器,产生 1 个周期的控制脉冲。

优点:

- 不需要计算发送信号最低要求的脉宽。

- 控制信号只需要翻转,不需要返回初始值。

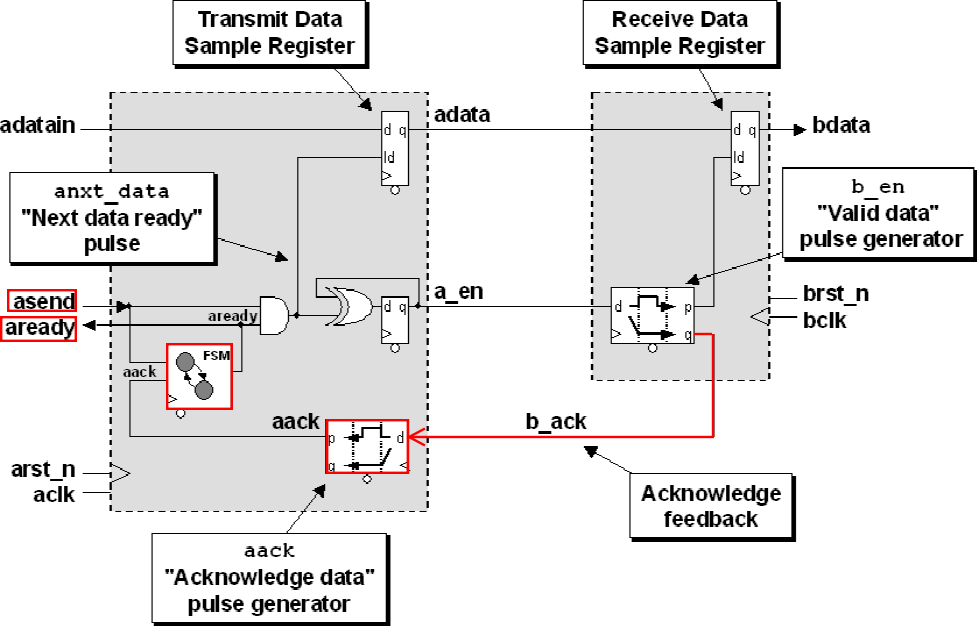

1 带反馈的 MCP

确认反馈信号 b_ack 生成确认脉冲 aack , aack 用作小型 READY-BUSY、1 状态 FSM 的输入,该模块生成就绪信号 aready 以指示现在可以安全地再次更改 adatain 数据和 asend 控制信号。

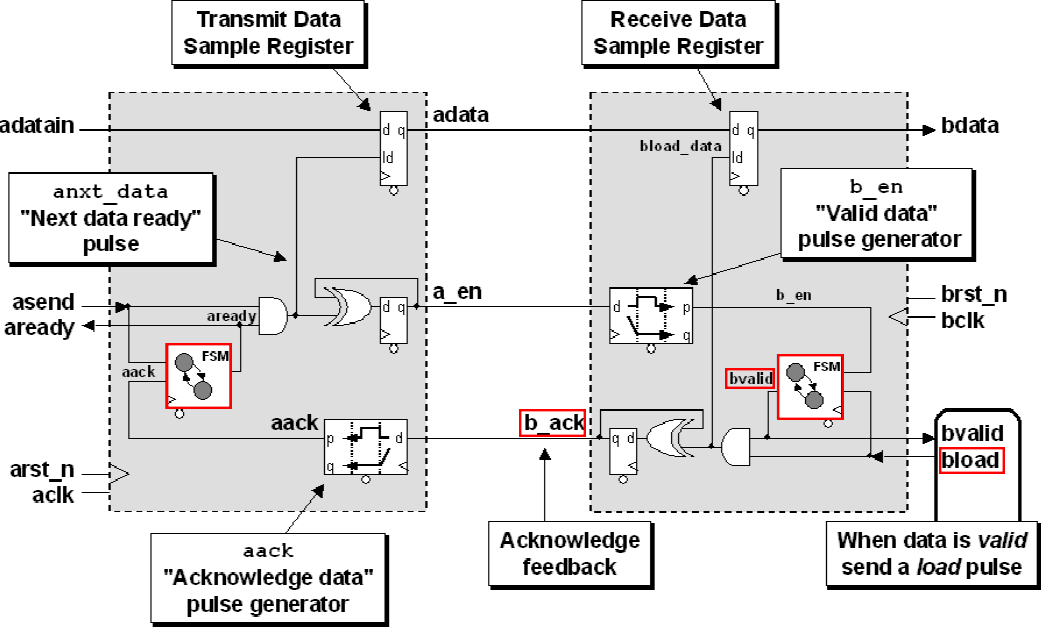

2 带 acknowledge 反馈的 MCP

接收时钟域有一个 WAIT-READY、1 状态 FSM,当数据寄存器的输入上的数据有效时,它会向接收逻辑发送有效信号 bvalid 。在接收逻辑通过断言 bload 信号确认应加载数据之前,不会实际加载数据。在数据加载之前,不会向发送时钟域提供反馈。加载后才会将 b_ack 信号发送回。

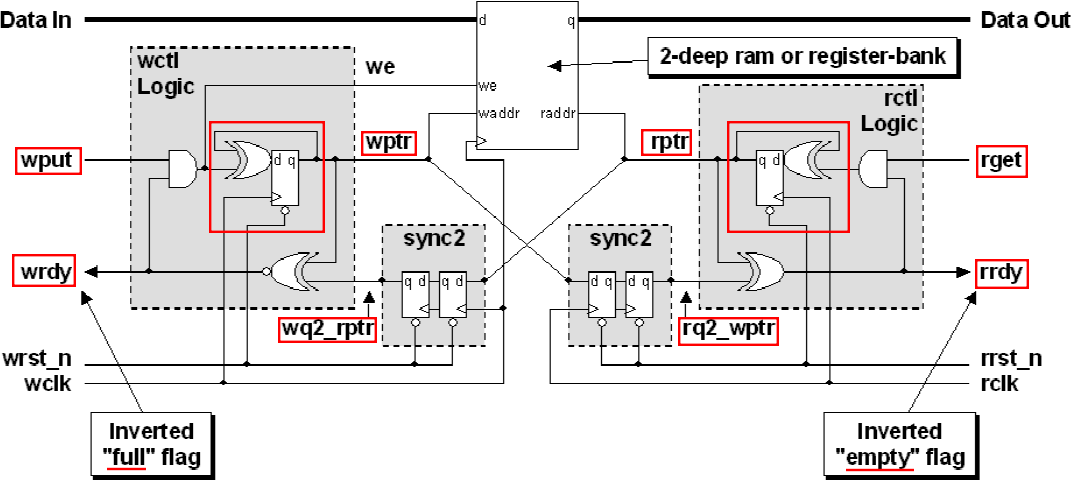

2 FIFO

计数器

对于计数器而言,跨时钟域传输时,通常不需要采样计数的每一个值(允许漏采样)。

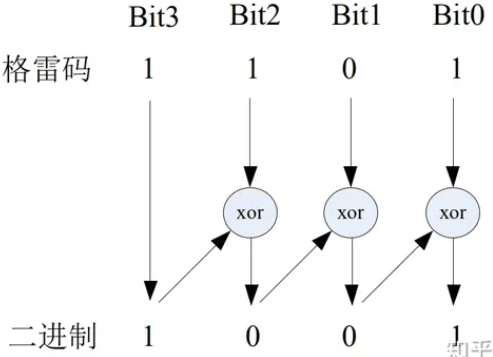

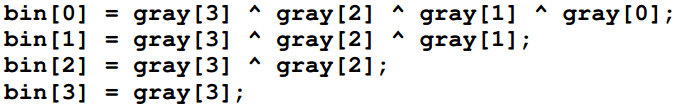

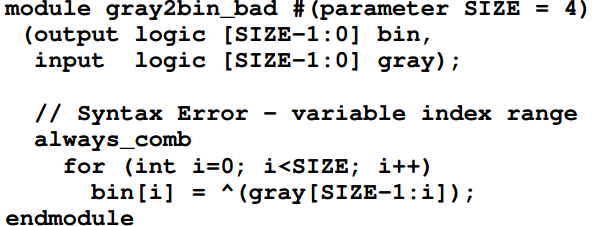

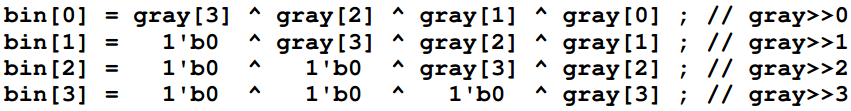

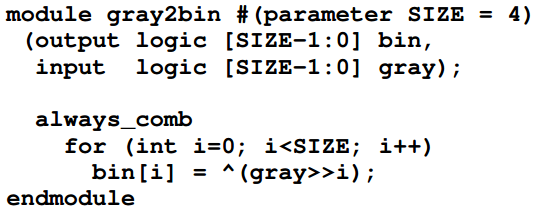

格雷码 -> 二进制码

- 原理:

- 简单赋值:

- for 循环:无法编译

- for 循环:可以编译

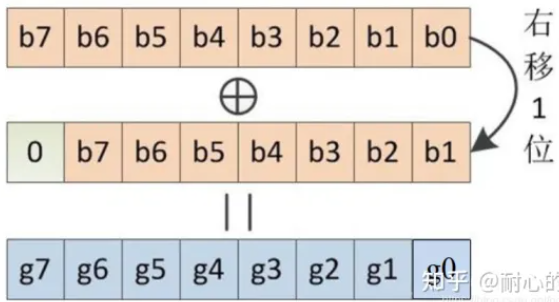

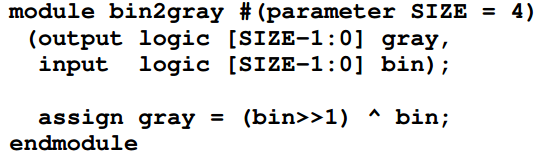

二进制码 -> 格雷码

- 原理:

- 右移异或:

二进制计数器

二进制计数器在计数时会发生多位同时变化,可能由于数据偏差导致错误采样。

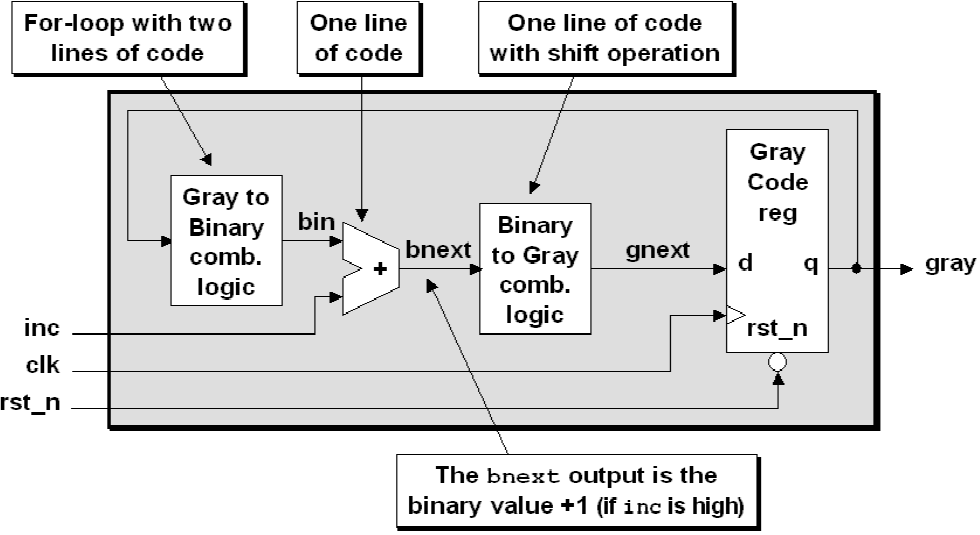

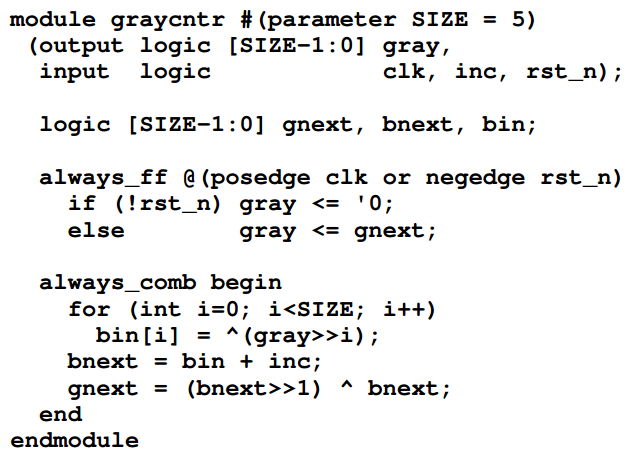

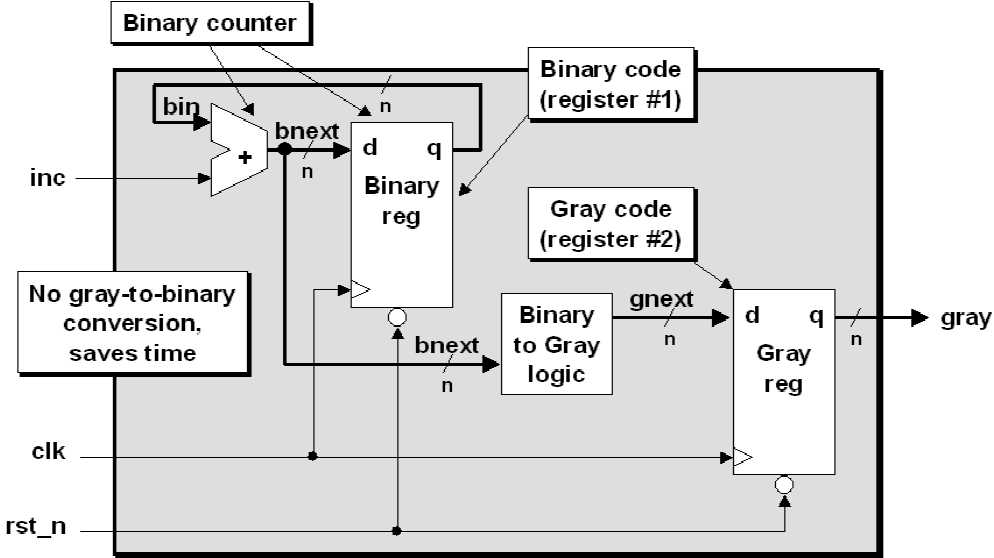

格雷码计数器

格雷码每次计数仅有一位发生变化,消除了多 bit CDC 问题。

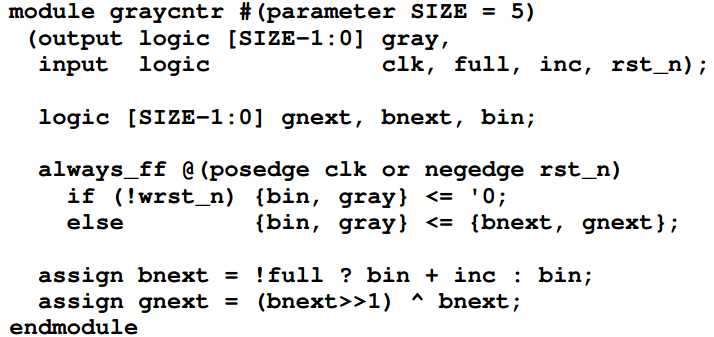

#1

#2

使用 2 个寄存器的 1 位深异步 FIFO

- 计数器:1 位深的格雷码/二进制码计数器只不过是一个翻转寄存器。

- 空/满标志:用翻转的 empty/full 表示 rrdy/wrdy 。

- 写入 1 个数据/控制信号后,FIFO 变满。此时 wptr 指向 RAM 的第二个地址,即 wrdy 有效后 wptr 已经指向可以写的地址;读端也是一样。

- 使用这种方法,我们能够从发送 MCP 中删除一个时钟周期,并从确认反馈路径中删除另一个时钟周期。(?)

命名约定和设计分区

命名约定

- 对于时钟信号及由其产生的信号,使用前缀字符来标识信号所处的时钟域。

设计分区

- 每个模块仅允许一个时钟。

- 设计时,将各模块划分为单时钟模块,便于 STA 分析。

- 使用同步器模块进行跨时钟域信号传输。