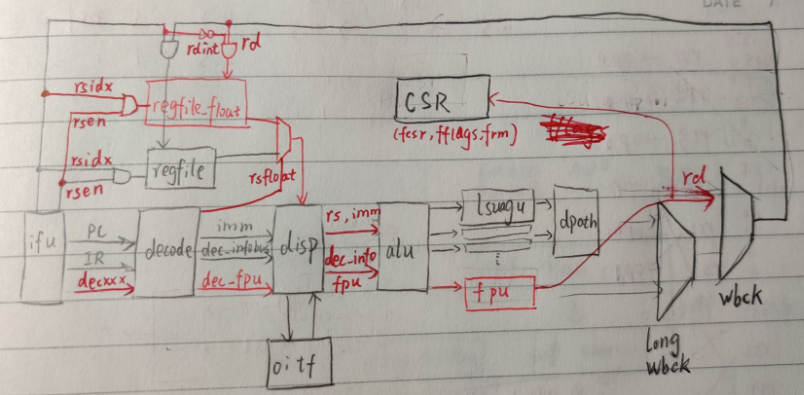

设计

- ifu 预先译码出 rsidx 和 rsen ,从整数寄存器堆和浮点寄存器堆取出操作数。

- decode 译码出 rsfloat ,对寄存器输出的操作数进行选择。

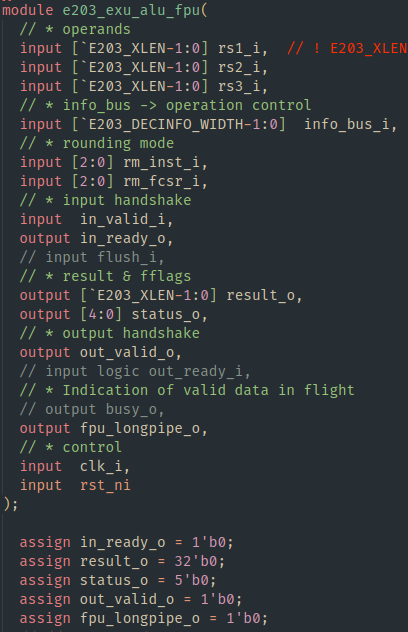

- decode 译码出 fpu 需要的相关信号。

- disp 将 rs 和 fpu 相关译码信号派遣给 alu 。

- alu 将 rs 和 fpu 相关信号派遣给 fpu 。

- fpu 计算得到 rd 和 fflags 。

- rd 通过 wbck 写回,根据 decode 得到的 rdint 信号选择写回到整数或者浮点寄存器堆。

- fflags 直接写回 csr 寄存器。

- 修改了 valid & ready 相关信号。

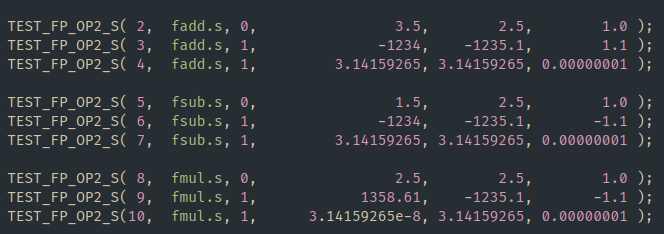

仿真

VCS

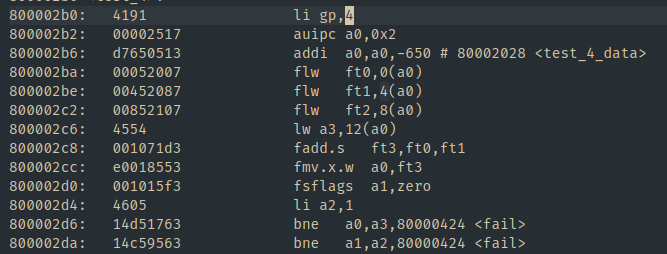

- 编译得到指令的机器码

- 将指令数据读取入 itcm ,执行指令

$readmemh({"/home/chms/Workbench/riscv/E203FV/riscv-tools/riscv-tests/isa/generated/rv32uf-p-fadd.verilog"}, itcm_mem);

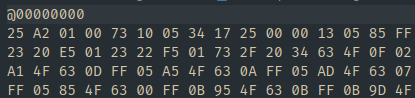

- 波形结果正确,并且浮点指令测试全部 PASS

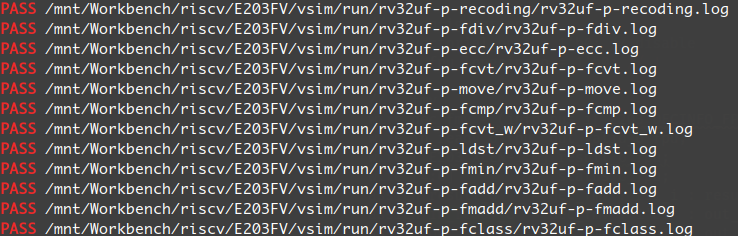

Vivado

vivado 对 sv 支持不足,有的语句无法识别,所以是仿真空的 fpu ,仿真整数指令。

整数加法指令正常(

15 + 11 = 26),结果 PASS

- 后仿真等等结果都是 PASS

综合

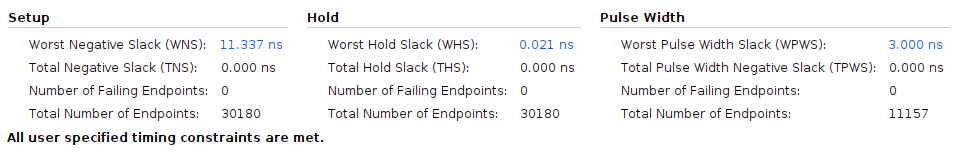

未修改 rtl 的综合时序

嵌入空 fpu 的综合时序

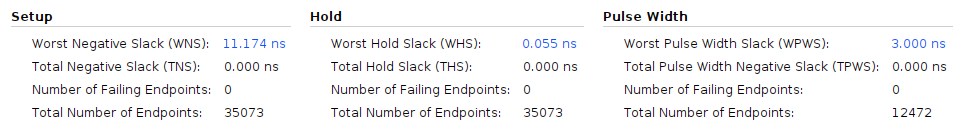

嵌入 fpu 的综合时序

holdtime slack 还提升了。

问题

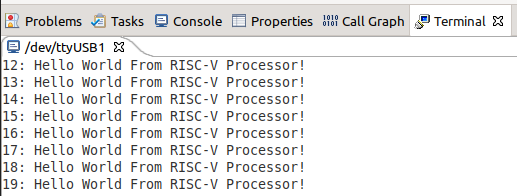

未修改的 rtl

运行 HelloWorld 程序,会有报错 TDO stuck high ,但是串口可以正常输出结果。

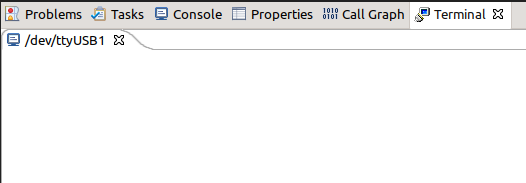

嵌入 fpu 的 rtl

运行 HelloWorld 程序,一样的报错信息,串口无输出。

嵌入空 fpu 的 rtl

运行 HelloWorld 程序,一样的报错信息,串口无输出。