IEEE 754

格式

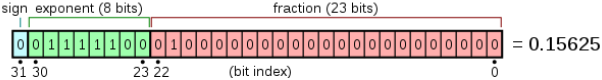

sign (1 bits):符号位

exponent (8 bits):指数位

bias:指数位偏移量,使指数位恒为正

exponent

[1, 254] -- (-bias) --> [-126,127]exponent = 0(全0) : subnormal number 非规格数

exponent = 255(全1) :non-number 特殊数

fraction (23 bits):尾数位

normal number:1.fraction(低位补0)

subnormal number:0.fraction(低位补0)

normal number 规格数

normal number = $sign * (1.fraction) * {2} ^ {(exponent - bias)}$

取值范围:$(-2 * {2} ^ {127}, -1 * {2} ^ {-126} U [1 * {2} ^ {-126}, 2 * {2} ^ {127})$

近似:$[-3.4 * {10} ^ {38}, -1.18 * {10} ^ {-38}] U [1.18 * {10} ^ {-38}, 3.4 * {10} ^ {38}]$

subnormal number 非规格数

subnormal number = [sign(+/-), exponent(全0,视为1), fraction]

subnormal number = $sign * (0.fraction) * {2} ^ {(1 - bias)}$

取值范围:$(-1 * {2} ^ {-126}, 1 * {2} ^ {-126})$

non number 特殊数

- Infinity = [sign(+/-), exponent(全1), fraction(全0)] ($\pm {2} ^ {128}$)

- NaN = [sign(+/-), exponent(全1), fraction(非全0)]

浮点加减

原码加减

浮点数尾数使用原码表示,因此涉及原码加减 $in1 \pm in2$

比较两个操作数的符号

- 加法:同号求和,异号求差

- 减法:异号求和,同号求差

求和:

数值位相加,若最高位产生进位则结果溢出;和的符号取被加/减数的符号

- $sign = sign[in1]$

- $f = f[in1] + f[in2]$ ,若最高位产生进位则结果溢出

求差:

$f = f[in1] + f[in2]_补$

- 最高数值位产生进位,表明加法结果为正,所得数值位正确。

- $sign = sign[in1]$

- 最高数值位没有产生进位,表明加法结果为负,得到的是数值位的补码形式,需要对结果求补。

- $sign = - sign[in1]$

- 最高数值位产生进位,表明加法结果为正,所得数值位正确。

移码加减

阶差:$[\Delta E]_补 = [E_x]_移 + [-[E_y]_移]_补$

浮点运算

浮点加减

$x = M_x * {2} ^ {E_x}, y = M_y * {2} ^ {E_y}$

$x + y = (M_x * {2} ^ {E_x - E_y} + M_y) * {2} ^ {E_y}$

$x - y = (M_x * {2} ^ {E_x - E_y} - M_y) * {2} ^ {E_y}$

1. 对阶

小阶向大阶对齐,阶小的那个数尾数右移,右移的位数等于$|\Delta E|$。

设$\Delta E = E_x - E_y$ :

$[\Delta E]_补 = [E_x]_移 + [-[E_y]_移]_补$

若$[\Delta E]_补 \leq 0$ :$E_x$ <- $E_y$ , $M_x$ <- [$M_x$ << ($E_x - E_y$)]

若$[\Delta E]_补 > 0$ :$E_y$ <- $E_x$ , $M_y$ <- [$M_y$ << ($E_y - E_x$)]

注:尾数右移按原码小数方式右移,符号位不参加移位,数值位要将隐含的一位 1 右移到小数部分,空出位补 0 。右移时,低位移出的位不要丢掉,应保留并参加尾数部分的运算。

2. 尾数加减

定点原码加减:要将隐藏位与附加位都还原参加运算。

3. 尾数规格化

加减后的尾数不一定是规格化的。

右规(1b.bbb…):尾数右移一位,阶码加 1 。

左规(0.00bb…):尾数逐次左移,阶码逐次减一,直到将第一位 1 移至小数点左边。

4. 尾数舍入

对阶和右规时,对尾数右移,低位移出的位要进行保留。

保护位 gurad :紧跟在尾数右边的一位。

舍入位 round :左规时可根据其值进行舍入。

粘位 sticky :只要舍入位的右边有任何非 0 数字,粘位就被置 1 ,否则置 0 。

舍入模式 rouding mode

就近舍入 RNE/RMM :舍入为最近可表示的数

多余位的值超出规定的最低有效位值 LSB 的一半,则应向最低有效位进 1,否则简单的截尾即可。对于恰好是的一半值的这种特殊情况,要根据当前的值来分别讨论若 LSB 现为 0 ,则简单的截尾;若 LSB 现为 1 ,则向 LSB 进1。

朝 0 方向舍入 RTZ:截取所需位数,舍弃后面所有位

简单地截尾。

朝 $-\infty$ 舍入 RDN :总是取左边最近可表示数

对正数来说,直接截尾。

对负数来说,多余位全为 0 则直接截尾,不全为 0 则向 LSB 进 1。

朝 $+\infty$ 舍入 RUP :总是取右边最近可表示数

对正数来说,多余位全为 0 则直接截尾,不全为 0 则向 LSB 进 1 。

对负数来说,直接截尾。

5. 溢出判断

指数上溢:结果指数超过了最大允许值(127)

指数下溢:结果指数超过了最小允许值()

溢出判断电路:

- 右规和尾数舍入

- 左规

双通道浮点加法

经过上面分析,双路径算法就应运而生了,M.J. Flynn 等人, 提出了双路径算法(Michael.J.Flynn,1990):

它的基本思想是根据两操作数的指数差异大小来划分数据通路。这是因为,当指数差异较小时,两指数进行减法操作时.其结果将可能产生大量的前导零,这在规格化的时候将产生大量的左移操作,而移位的位数是个变量:当指数差异较大时,又将在对齐指数时产生大量的移位。浮点加法器的双数据通道划分方法在浮点加法器的结构设计中被广泛采用。